使用Virtex-5 FPGA實現LTE仿真器

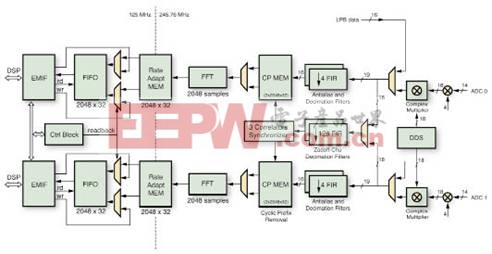

中頻數據隨后進入下行鏈路FPGA,由該FPGA將其轉換為基帶并進行過濾。即便芯片速率保持在245.76MHz,多相抽取濾波器仍能以30.72MHz的符號率進行奈奎斯特FIR濾波、頻譜鏡像抑制和數據率降低等操作。

FPGA輸入數據流看上去像數據流,而非一系列的OFDM符號。同步函數對數據流進行適當的切分,從而描繪出OFDM符號。(要實現這一點,同步線路必須使用多個相關器在深度抽取的輸入數據中檢測出Zadoff-Chu主同步信號,隨即才能獲取OFDM符號。)最后,在刪除循環前綴后,以FFT轉換獲得的最終數據則通過EMIF接口傳遞到另一個DSP。下行鏈路包含兩個以串行RapidIO接口連接在一起的DSP。這兩個DSP的作用是進行頻率校正、信道估計、均衡和MIMO解碼。然后由這兩個DSP在MAC層互連之前,進行數據通道和控制通道抽取、Viterbi和Turbo解碼、去交織和解擾。

在上行鏈路側,由第三個FPGA負責上行鏈路和下行鏈路FPGA之間的回送測試,確保SDR模板符合CPRI/OBSAI標準。

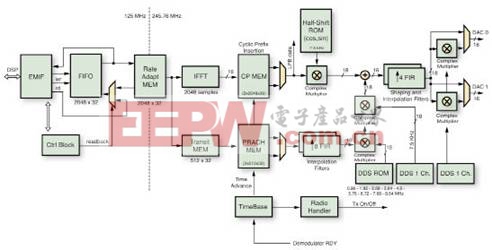

我們的設計小組廣泛使用賽靈思Core GeneratorTM IP核來生成濾波器、DDS、FFT、Block RMA、FIFO 和MACC功能,把DSP48E和DCM用于設計中的時鐘去歪斜部分。這種大規模例化方法在縮短開發時間的同時,還能夠提供緊湊設計方案。圖3為“上行鏈路FPGA”實現反向FFT、循環前綴插入、濾波、IF上變頻轉換以及其他時分雙工和PRACH處理所需的操作。該系統將同一信號發送至兩個DAC以備冗余。

因為這個項目的市場投放時間要求非常緊迫,我們對其功能劃分進行了精心分析。FPGA應該容納甚至更多的LTE功能,不過我們的設計目標在于尋求系統中FPGA與DSP部分間的平衡。

FPGA設計策略

該項目的市場投放時間要求非常緊迫,因此我們對FPGA和DSP之間的功能劃分進行了精心的分析。值得注意的是,FPGA應能夠支持更多的LTE功能,不過我們的設計目標之一是尋求系統中FPGA與DSP部分間的平衡。

圖3 “上行鏈路FPGA”

FPGA時鐘頻率是設計中較為困難的一環。在像調制系統這樣的大型設計中采用245.76MHz的時鐘速率是項艱巨的任務。我們設計小組需要考慮許多問題,比如功耗、設計約束、布局布線等。盡管如此,由于ISE®設計套件可提供各個設計迭代的穩定高質量結果,過采樣因子(FPGA時鐘頻率與OFDM符號頻率之比)為8,能夠讓諸如濾波器和FFT轉換這樣的設計項目在盡量少的條件下滿足所需的LTE功能。ISE軟件也幫助我們實現了合適的同步電路面積。我們設計的關鍵在于在上行鏈路中采用射頻卡架構(而非存在I/Q不平衡缺點的直接轉換法)來接收來自中頻的FPGA數據。通過使用賽靈思直接數字頻率合成器(direct digital synthesizer),18位正弦/余弦波可用作復雜調制工作的理想載波,并可用在傳輸無線電信號上測得的誤差矢量幅度予以確認。由于采用了賽靈思Virtex-5 FPGA和TI的DSP技術,LSU UeSIM LTE仿真器已經成為蜂窩網絡最先進的載荷-應力解決方案測試設備,能為SDR系統提供強大、靈活和可擴展的解決方案。

圖4為前端“下行鏈路FPGA”進行IF下變頻轉換、多相抽取濾波、同步、循環前綴刪除和直接FFT等操作。該系統使用了兩個鏈路來支持TDD和FDD模式的MIMO操作。

圖4 前端“下行鏈路FPGA”本文引用地址:http://www.104case.com/article/191438.htm

評論