基于DS28E01的FPGA加密認證系統的設計

唯一識別號及附加數據(常數)在內的 HASH運算結果,運算的結果是 160位的 MAC(消息認證碼),同時,FPGA內部也會同安全存儲器一樣進行包含密鑰、隨機數、附加數據及器件識別號在內的 HASH計算并產生一個期望的MAC。然后,在 FPGA內會對這兩個 MAC進行比較,如果一樣,則 FPGA認為該電路是“合法”電路,因為它擁有正確的密鑰。此時 FPGA進入正常工作狀態,開啟/執行其配置數據中的所有功能,會執行所有的功能。如果 FPGA和DS28EO1兩者產生的MAC不匹配,則系統會認為該電路是一個“非法”電路,因為該系統不具有正確的密碼。此時 FPGA進入非正常運行狀態,只執行有限的功能。

3.2、加密認證模塊的程序設計

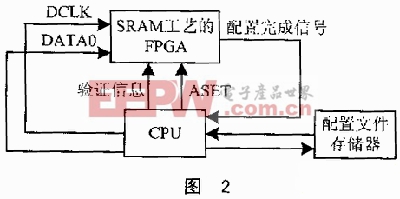

為了實現加密認證的功能,我們在 FPGA中利用 VHDL語言設計了 IFF模塊,在 IFF模塊的內部是根據SHA-1算法實現了對輸入密碼的HASH函數運算以及與DS28E01中產生的MAC的比較功能,IFF模塊的接口定義如圖 2所示:

其中,CLKIN是一個大于 20M的時鐘;IFF是認證啟動信號,在 IFF信號上升沿的時候模塊內部開始啟動 HSAH運算過程以及密碼比較過程;RESET是復位信號,高電平有效;IB則是 FPGA通過 1-Wire協議與 DS28E01通訊的信號;FOE信號是 IFF模塊的輸出線,在IFF內部 MAC比較完成后,如果 FPGA認定該電路具有正確的密碼,則會置 FOE信號為低電平,反之如果 FPGA認定該電路不是合法的電路,則會置 FOE信號為高電平,在 FPGA內部可以根據FOE的信號來實現不同的功能。這樣,系統就可以根據電路是否是被拷貝的來實現不同的功能,防止了設計被拷貝。

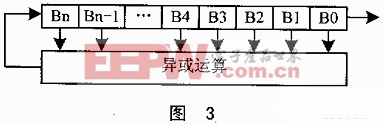

在 IFF模塊中,實現了標準的 SHA-1算法,其中算法流程圖見圖3,在 FPGA配置完成之后,在 RESET信號與時鐘信號的控制下,FPGA內部就會運行 SHA-1算法產生相應的MAC,與由 DS28E01產生的 MAC進行比較,根據比較結果將 FOE設置為不同的狀態,然后 FPGA就可以根據 FOE的狀態來判斷是否是合法電路。其中的初始化主要完成消息填充和附加原始消息長度以及在算法中需要的函數和常數的定義。

圖 3 SHA-1算法流程圖(Figure 3. SHA-1 algorithm flow)

4、設計總結

在現在電子設計的成本越來越高的情況下,基于 SRAM的 FPGA由于自身限制,容易使得設計者的設計被復制,從而給設計者提出了設計具有加密功能的電子系統,由于 SHA-1 算法引擎的 DS28E01芯片作為加密認證系統的核心芯片,并利用 DS28E01針對 Xilinx公司的 X3CS500E開發了實際的加密認證系統,并將此系統應用于實際的產品中,取得了良好的效果。

本文作者創新點:針對基于 SRAM的 FPGA在配置過程中設計數據容易被克隆的現象,設計了基于安全存儲器的加密認證系統,增強了系統的安全性。

評論