基于FPGA的AD7862接口電路設計

2 接口電路程序設計

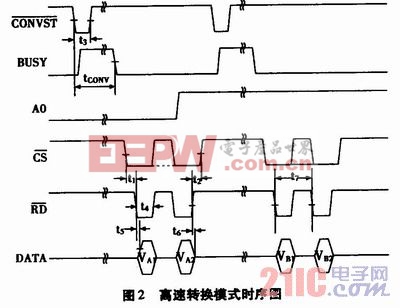

在本設計中用的是AD7862-10,采用高速轉換模式,典型轉換時序如圖2所示。

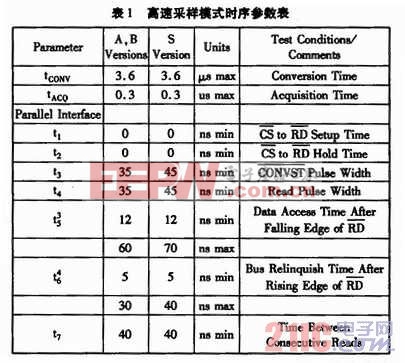

圖2中隊應的時間參數的要求如下表1所示。

從圖2的時序圖可以看出AD7862通過輸入脈沖信號CONVST啟動轉換。在CONVST信號的下降沿,片上的兩個track/hold都同時的被設置為hold狀態,兩個通道開始進行轉換。轉換時鐘由內置的晶振提供。BUSY信號指示轉換結束,同時兩個通道的轉換結果可以被讀出。由AO的值來決定第一次讀取的值是VA1或者VB1,第二次讀取的是VA2或者VB2。當CS信號和RD信號為低時,數據被從12位的并行數據線上讀取。在高速轉換模式下,AD7862的轉換時間為3.6 us,track/hold收集時間為0.3 us。為了保證最佳轉換效果,在轉換期間和下一次轉換開始前300 ns不能進行讀取操作。

上述的時序圖對應為先讀取VA1和VA2,然后在讀取VB1和VB2,對應的信號AO首先被設為低電平,然后被拉為高電平。在設計驅動電路的過程中,一定要保證設計的時序滿足上述時序參數的要求,不然就有可能發生采樣不準,出錯。

結合AD7862的轉換速度,FPGA選擇1O MHz的處理時鐘。對于整個轉換過程的控制用一個狀態機來完成,狀態機分為12個狀態 (idie,convert1,busy1,reada1,wait1,reada2,swapchna1,convert2,busy2,readb1,wait2,readb2),其中idle狀態為空閑等待轉換狀態;convertl指示第一次轉換啟動狀態;busyl指示第一次轉換狀態;resdal狀態下讀取 VA1;waitl狀態為讀取VA1和VA2之間的等待狀態;reada2狀態下讀取VA2;swapchnal狀態指示交換到另一個通道進行轉換;convert2指示第二次轉換啟動狀態;剩余狀態和前面的類似,只不過是針對VB1和VB2而言。設計代碼如下(只描述VA1和VA2的部分,剩下的類似):

評論