一種基于FPGA 的驅動接口電路的設計

AD7862—2被用于單極0 到2. 5 V 的輸入范圍。對AD7862—10和AD7862-3來說, 轉換輸出的12位為二進制補碼, 對于AD7862-2來說, 輸出的為12位的原碼。

2、接口電路程序設計

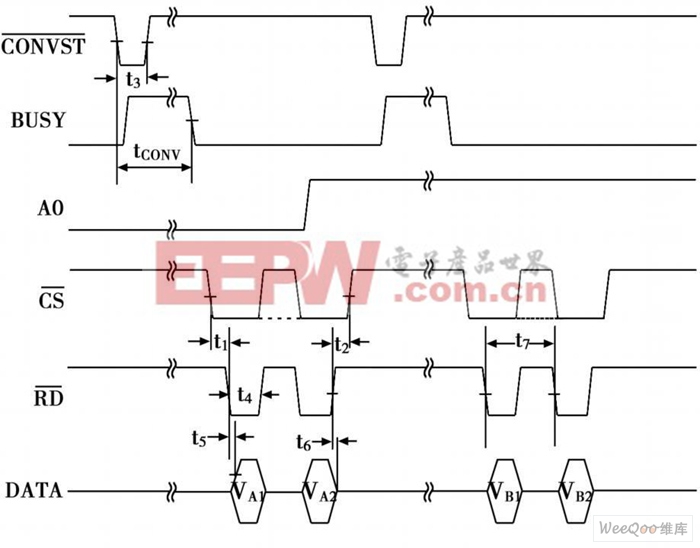

在本設計中用的是AD7862??10, 采用高速轉換模式, 典型轉換時序如圖2所示。

高速轉換模式時序圖

圖2高速轉換模式時序圖。

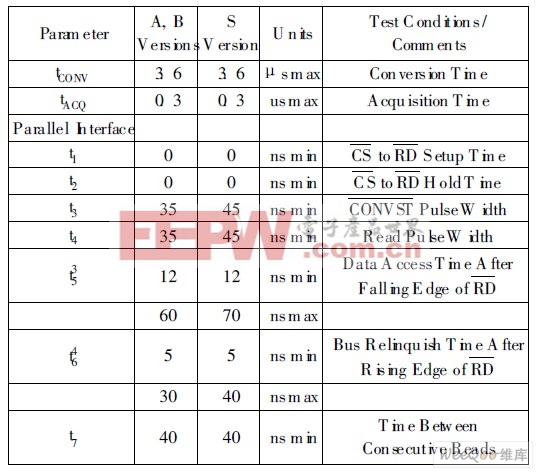

圖2中對應的時間參數的要求如下表1所示。

表1高速采樣模式時序參數表。

高速采樣模式時序參數表

從圖2的時序圖可以看出AD7862 通過輸入脈沖信號CONVST啟動轉換。在CONVST 信號的下降沿, 片上的兩個track /ho ld都同時的被設置為ho ld狀態, 兩個通道開始進行轉換。轉換時鐘由內置的晶振提供。BUSY 信號指示轉換結束, 同時兩個通道的轉換結果可以被讀出。由A0 的值來決定第一次讀取的值是VA1 或者VB1, 第二次讀取的是VA2或者VB2。當CS信號和RD信號為低時, 數據被從12位的并行數據線上讀取。在高速轉換模式下, AD7862 的轉換時間為3. 6 us, track /ho ld收集時間為0. 3 us。為了保證最佳轉換效果, 在轉換期間和下一次轉換開始前300 ns不能進行讀取操作。

上述的時序圖對應為先讀取VA1和VA2, 然后在讀取VB1和VB2, 對應的信號A0首先被設為低電平, 然后被拉為高電平。在設計驅動電路的過程中, 一定要保證設計的時序滿足上述時序參數的要求 , 不然就有可能發生采樣不準, 出錯。

評論