高階累積量調制識別改進算法的FPGA實現

2.3 微分后參數提取模塊

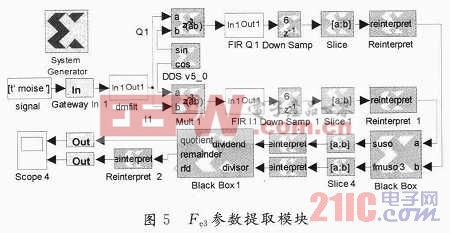

提取特征參數Fe3的模塊,如圖5所示。其中,dmfilt是微分中值濾波模塊,兩個Black Box是計算特征參數Fe3的模塊。待識別調制信號經過dmfilt模塊后,然后由DDS,FIR,DowSamp等提取同向分量和正交分量,再通過計算Fe3的模塊計算參數,最后結果由Scope輸出。

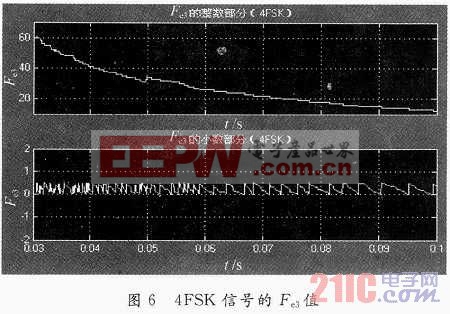

圖6是當信號為4FSK時,計算得到的Fe3值。其中,O.03~O.1 s是模塊計算參數的過程,O.1 s時對應的數據是計算的最終結果。將結果輸出到Matlab變量空間workspace中,可以得到在0.1 s時計算的Fe3值為12.4。

3 實驗結果

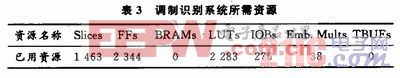

為了驗證調制識別系統的可行性,分別在Simulink和目標開發板上運行該設計。在產生硬件協同仿真模塊之前,先調用Resource Esti-mator模塊對本系統所需資源進行估測。估測結果見表3。

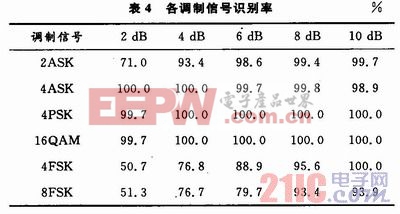

由于所需芯片內部資源較多,所以選用Virtex4-xc4vlx200芯片。然后在System Generator模塊中點擊Generate產生硬件協仿真模塊,并將它拖入到設計文件當中。給Virtex-4目標板上電,連接好JTAG口,啟動硬件協同仿真。當信號分別為2ASK,4ASK,4PSK等調制信號時,測試整個設計系統判決的結果,并將1 000次獨立試驗得到的仿真結果取平均,得到各種調制信號的識別率,如表4所示。從試驗結果來看,調制識別系統設計的FPGA硬件協同實現與Simulink仿真的結果基本一致,達到了設計的要求,從而也說明了System Generator有很高的精度。

4 結語

本文采用高階累積量改進算法對各種數字信號進行調制識別,大大提高了低信噪比環境下2ASK,4ASK,4PSK和16QAM信號的識別率,并在 System Generator中實現了高階累積量改進算法的FPGA設計,從模型的建立到FPGA的實現都是在圖形化設計環境下完成的,避開了編寫復雜VHDL語言的環節,且轉化到FPGA上實現的性能好,設計過程簡便靈活,從而為調制方式識別算法的設計提供了一種新的方案。利用System Generator提供的圖形化建模環境和自動轉換成VHDL代碼的能力,設計者可以將更多的時間和精力放在算法的優化上,同時又能顯著縮短設計開發周期。

本文引用地址:http://www.104case.com/article/191395.htm

評論