基于DSP Builder數字信號處理器的FPGA設計

2.4 基于Simnlink的系統VHDL代碼生成

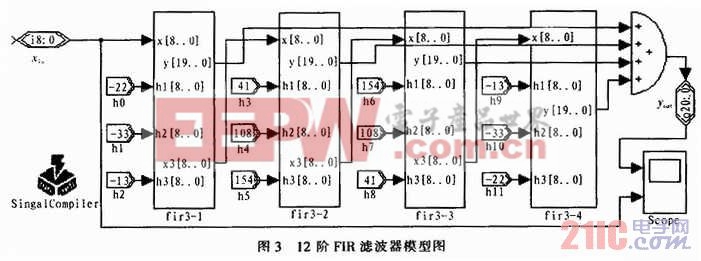

完成模型設計后,先在Simulink中對模型進行系統仿真,即通過Simulink中的2通道示波器Scope模塊查看仿真結果。DSP Builder可提供QuartusⅡ軟件和MATLAB/Simulink工具之間的接口,即Signal Compiler模塊。

若通過系統仿真,該系統已達到設計要求,雙擊SignalCompiler模塊,設置好相關參數后,即可將模型文件.mdl轉化為硬件描述語言文件.vhd,并可對其進行綜合。之后在OuartusⅡ環境中,打開DSP Builder,建立的QuartusⅡ工程文件,就可以對生成的VHDL代碼進行器件配置、引腳設定、編譯、時序仿真、硬件下載等工作。

2.5 基于QuartusⅡ的時序仿真

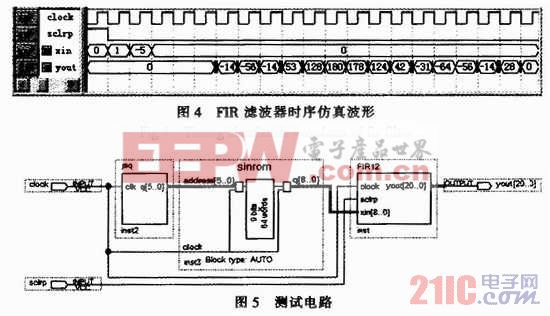

在Simulink中進行的系統仿真是針對算法實現的,與目標器件和硬件系統沒有關系,其仿真結果并不能精確反映電路的全部硬件特性,因此,需要對設計進行時序仿真。

在QuartusⅡ環境中,打開DSP Builder建立的QuartusⅡ工程文件,對上述的VHDL代碼進行時序仿真。圖4為在OuartusⅡ7.O環境下FIR數字濾波器時序仿真圖。圖4中clock為系統時鐘,sclrp為清零信號,xin為輸入數據,yout為濾波器的輸出結果。

由式(2)知:若xin{1,-5},h(n)={-22,-33,-13,41,108,154,154,108,41,-13,-33,-22},則濾波器的輸出yout的理論結果為:yout=xinh(n)={-14,-56,-14,53,128,180,178,124,42,-31,-64,-56,-14,28}。可見,所設計的FIR數字濾波器在QuarmsII 7.0中進行時序仿真得到的輸出結果和理論上計算得到的結果是完全一致的。

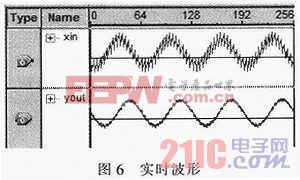

3 實際硬件測試

只進行工程軟件仿真遠遠不夠,還必須進行硬件實時測試。在硬件實際運行時,可以從外部信號源接入器件內部或者在其內部存儲正弦波數據。這里采用后者,即在頂層文件中引入LPM_ROM宏模塊,在其中存入頻率分別為0.5和8 kHz2個正弦波迭加信號數據的.hex文件.FIR濾波器模塊直接從ROM中讀取數據,測試電路如圖5所示。

在QuartusⅡ環境中,對測試電路進行編譯,下載到cyclone系列EP1C12Q240C8器件后,就可以對硬件進行測試。采用Ahem公司的Signal-TapⅡ嵌入式邏輯分析儀進行芯片測試,用戶無需外接專用儀器,就可以通過FPGA器件內部所有信號和節點的捕獲對系統故障進行分析和判斷,而又不影響原硬件系統的正常工作。

經嵌入式邏輯分析儀得到的實時波形如圖6所示。實際測試發現,經過設計的低通濾波器后,高頻信號被濾除,只有低頻信號輸出,濾波效果滿足系統要求。需要注意的是,SignalTapⅡ嵌入式邏輯分析需工作在JTAG方式,在調試完成后,需將SignalTapⅡ移除設計,以免浪費資源。

4 結束語

由以上設計過程可知,基于Matlab/Simulink/DSP Builder/OuartusⅡ的設計流程,可以幫助設計者完成基于FPGA的數字信號處理系統設計。使用相對獨立功能的電路模塊和子系統進行模塊化的設計,避免了繁瑣的VHDL語言編程;設計者只要對DSP Builder模塊庫中相應模塊的基本參數進行簡單設置,而不需要對各模塊具體的實現過程進行詳細了解,甚至不需要了解FPGA本身和硬件描述語言,極大縮短了開發周期。而且隨著技術的發展,FPGA的性能越來越高,價格則逐步降低,芯片的處理速度更快,片內資源更大,這將給FPGA在信號處理領域的應用提供更為廣闊的空間。

評論