基于FPGA的擴頻測距快速捕獲仿真研究

2 主要模塊仿真結(jié)果

2.1 PH碼產(chǎn)生模塊

本設(shè)計選取的PN碼為63位,本征多項式為x6+x+1。該PN碼產(chǎn)生器由VHDL語言編寫,其仿真結(jié)果如圖2所示。本文引用地址:http://www.104case.com/article/191337.htm

2.2 FFT轉(zhuǎn)換模塊

該模塊是本設(shè)計的核心模塊,由輸入緩沖器、FFT運算器、控制器構(gòu)成,完成對數(shù)據(jù)的FFT變換。將PN碼發(fā)生器產(chǎn)生的數(shù)據(jù)存入輸入緩沖器中,在控制器的控制下,F(xiàn)FT運算模塊從輸入緩沖器中讀取出數(shù)據(jù)值進行FFT變換,然后得出輸出數(shù)據(jù)。圖3所示為FFT模塊的輸入輸出關(guān)系。fft_imag_out,fft_real_out分別為輸出數(shù)據(jù)的實部、虛部和修正因子,m_soutoe_sop為輸出數(shù)據(jù)的起始位。

2.3 計算模塊

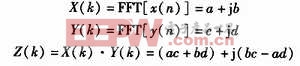

設(shè)兩路信號進行FFT后的數(shù)據(jù)為

可見對進行FFT變換后需要進行的運算處理其實質(zhì)是一個乘加,一個乘減和一個加法運算,其中乘加運算仿真結(jié)果如圖4、圖5所示。

評論