基于ARM和CPLD的可重構檢測系統設計

2.1芯片選擇

ARM 選用內嵌ARM920T核的EP9315微控制器, CPLD選用Alter公司MAX II系列芯片EPM1270。其中, EP9315具有最高可達200MHz的工作頻率、16KByte指令緩存、16KByte數據緩存和單/雙精度整數及浮點處理能力,還集成了大量適用的外部接口,如IDE接口、USB接口和LCD接口等;EPM1270 型CPLD 含有1270邏輯元件、100多個可用I/O 引腳,每個IO口都可配置成TTL、LVTTL、CMOS、LVCMOS和施密特觸發器模式。以上兩芯片均為低成本、低功耗芯片。

2.2 CPLD的內部結構設計

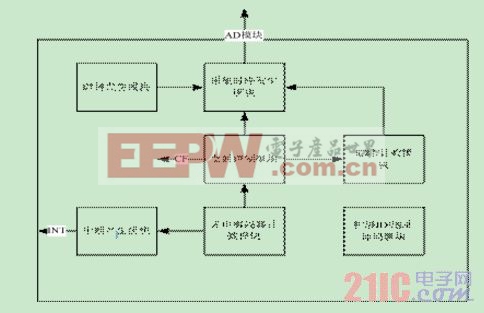

在該系統中ARM作為主芯片,負責復雜的數據處理、人機交互、圖形顯示和接口通信等任務,如何合理設計CPLD外部接口和內部結構,將直接影響到系統的功能和可重構程度。CPLD內部結構如圖2所示, 它包括時鐘發生器、4個定時計數模塊、發射脈沖發生模塊、采樣時序發生模塊、光電編碼計數模塊和中斷產生器, 可進行閉環/開環檢測。本文引用地址:http://www.104case.com/article/191335.htm

圖2 CPLD內部結構圖

2.3 高速板間設計的信號完整性問題分析

為了使該系統架構具有可重構性,筆者將該系統設計成多PCB結構,以ARM作為主芯片的系統板作為主板,以CPLD為核心的擴展板作為背板,由于這個系統為高速系統,這樣的設計必將帶來信號完整性問題。其中最主要的是信號長距離傳輸導致信號質量下降和“地彈”現象的產生。

背板設計必將大大增加信號的傳輸距離,使得信號的質量受到很大影響,筆者在設計中使用信號線上增加數據緩沖器進行隔離和選擇源端電阻匹配等方式,很好的解決了信號的有效傳輸問題。

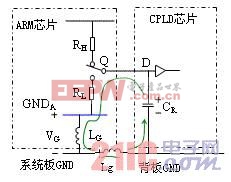

我們根據實際情況建立如下地彈模型圖,如圖3所示。從圖3中可以看出在ARM芯片邏輯門迅速切換的時候,將引起很大的瞬態電流,由于兩板之間的電源連接線上的分布電感Lg的存在,將導致嚴重的“地彈”現象。根據地彈電壓

V=Lg×dI/dt

可知,地彈電壓與電源連接線上的分布電感和瞬態電流的大小成正比。因此我們對兩板之間的電源連接方式作處理,增加回流導線的面積,盡量減小回流導線的長度,使得回流路徑上電感盡量小;同時在信號線上增加抑制瞬態電流的電阻,試驗結果表明這種設計較好地解決了電源的完整性問題。

圖3 地彈模型圖

3結束語

本文介紹了一種基于ARM+CPLD 結構的可重構檢測平臺的設計方法, 并基于此方法開發了一臺用于鋼板、鍛件和基樁等檢測的試驗樣機。此方法以模塊化的方式將ARM及CPLD技術巧妙的結合起來,使基于此方法構建的檢測儀器兼有ARM 和CPLD兩者的優勢,實現了部分控制算法的硬件。與傳統的基于MCU 的檢測設備相比,具有實時性好檢測速度高、外圍器件少、兼容性和擴展性好等諸多優點;并具有硬件方案的可重構性, 又更方便于客戶的應用開發,且成本低。經現場實驗驗證,該檢測設備大大提高現場檢測的速度和智能化。由于該設計方案具有極其靈活的可重構性,所以稍加修改擴展就可應用于其他檢測系統中去。

本文作者創新點: 提出了一種基于ARM+CPLD結構的可重構檢測系統的設計方法。并根據這一方法開發了一款新型聲波檢測儀,提高了現場測試的自動化程度。

評論