基于FPGA的測角脈沖細分電路的設計

2 基于FPGA的脈沖細分電路的設計

2.1 總體設計

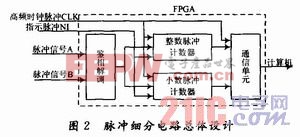

大部分的角度傳感器輸出信號都是由兩路相位差90°的脈沖信號組成,設計電路時首先可以對兩路信號進行鑒相解調與倍頻,一方面完成轉向的判斷,另一方面將兩路信號四倍頻;接著設計整數脈沖計數器、小數脈沖計數器,對相應脈沖數進行計數;最后將計數值通過串口通信單元順序發送至計算機,方便后期的數據處理。這里最為關鍵的問題是利用脈沖細分技術計出被測脈沖的小數部分,另外指示脈沖對計數器的控制精度關系到計數值的準確與否,因此要利用性能良好的硬件并巧妙地設計程序。這里硬件選擇了FPGA,程序則是利用HDL語言進行編寫,脈沖細分電路總體設計如圖2所示。

2.2 整數脈沖計數器

為了更準確地對倍頻后的脈沖進行計數,在設計時,電路采用了2個計數器輪流計數,指示脈沖控制2個計數器交替工作。具體方法是將兩個計數器的使能信號分別設置為1和0,由指示脈沖控制使能信號,在每一個指示脈沖到來時使能信號取反。另外,由于計數值很大,為了保證數值不會溢出,使用32位計數器。

2.3 小數脈沖計數單元

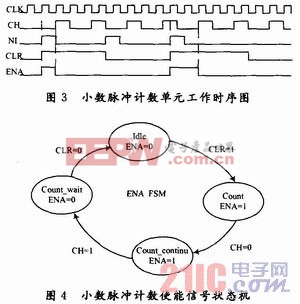

由脈沖細分技術可知,小數脈沖計數單元是要對指示脈沖上升沿與在其之后的第一個測角脈沖上升沿之間的高頻計數時鐘脈沖計數。測角脈沖信號是周期性的,而設計時要用到的只是指示脈沖之后的第一個陀螺信號的上升沿,這給小數脈沖計數的設計帶來了困難,在設計時使用了有限狀態機。這里主要利用整數脈沖計數單元中設計的整數計數器使能信號CLR與測角脈沖信號CH的狀態組合來設計狀態機,利用狀態機輸出小數脈沖計數器的工作使能信號ENA,這里狀態都是在時鐘CLK上升沿轉換。圖3與圖4分別為小數計數器工作時序圖與使能信號狀態機。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論