高精度DDFS信號源FPGA實現

另外,從圖中可以看出,實際上地址輸出信號是一組頻率為正弦信號頻率兩倍的三角波信號。可見,在產生正弦信號輸出的同時,還可以產生一組2倍頻的三角波輸出信號,只需取地址位的高12位作為輸出即可。

2)2-ASK、2-FSK、2-PSK數字調制信號 要產生2-ASK、2-FSK、2-PSK等數字調制信號比較容易。只需將數字基帶信號在其傳輸時鐘信號的作用下,逐位輸入模塊,用基帶數字信號的‘1’和‘0’來選擇不同幅度、頻率或相位的正弦信號輸出即可。

2-ASK信號:用3.125 MHz的信號表示數字信號的‘1’,用輸出幅度為0表示數字信號的‘0’。

2-FSK信號:用3.125 MHz的信號表示數字信號的‘0’,用582.077 kHz的信號表示數字信號的‘1’,如圖3所示。本文引用地址:http://www.104case.com/article/191312.htm

2-PSK信號:用初始相位為0的正弦信號的‘1’,用初始相位為180°的信號表示數字信號的‘0’。如圖4所示。

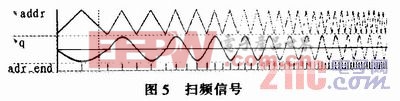

3)掃頻功能 掃頻功能的實現是通過改變步進來實現的。每產生一個周期的正弦信號以后,將步進遞加,為便于觀測,設計中設置S初始值為(50 000 000)10,步進遞增幅度為(10000000)10,實現了掃頻功能,掃頻起始頻率為582.077 kHz。掃頻步進約116.415 kHz,掃頻信號如圖5所示,同時可以提供各頻率信號的同步信息。只要改變步進初始值及遞增幅度即可完成更寬掃頻范圍及掃頻步進更佳的掃頻信號。事實上,FM信號也可以通過對輸出信號的步進的控制來加以實現。

5 硬件電路的實現

設計的最終目的是為了用硬件實現電路,因此,還要設計輸入步進設置及模式選擇的鍵盤模塊、頻率設置數據顯示模塊等VHDL程序模塊;后級的低通濾波網絡,功率放大電路等等。完成這些工作,即可完成一個完整的DDFS信號源的設計與制作。

6 結束語

本文的創新點為對DDFS設計進行優化,充分利用Cyclone II系列FPGA的片上資源,產生了最高頻率可達9.312 5 MHz.最低頻率分量及頻率分辨率低至MHz量級的正弦信號。通過進一步優化DDFS各模塊的性能,如減少相位累加器、數據取補碼等模塊的運算時間,進一步提高系統工作的最高頻率;進一步優化后級濾波網絡的特性等,就可以獲得性能曲線更平滑,輸出頻率更高,帶負載能力更強的優質的信號源。同時還可以增加FFT算法模塊,對信號進行頻譜分析等其他功能。

評論