基于PCD656的高速PCI總線接口的設(shè)計與實現(xiàn)

4 局部總線端設(shè)計

本設(shè)計中,局部總線端采用了C模式。C模式下可配置3種數(shù)據(jù)傳輸方式:單周期方式(Single Cycle Mode)、4字方式(Brust-4 Mode)和連續(xù)突發(fā)傳輸方式(Continuous Mode),在本設(shè)計中采用了連續(xù)突發(fā)方式,可以有效地提高輸出效率。

PCI9656在局部總線為為主設(shè)備,始終占用局部總線,局部總線端的FPGA始終響應(yīng)PCI9656的操作。方案中使用PCI9656的DMA傳輸模式,在本地端不需要進行地址譯碼,因此可以對PCI9656的控制信號進行簡化處理,PCI9656的局部端主要控制信號如下

ADS#:一次總線訪問開始;

Blast#:總線訪問結(jié)束;

LW/R#:讀寫控制信號;

Ready#:從設(shè)備準(zhǔn)備好信號,有效時表示總線訪問進行中;

LHOLD:PCI9656占用本地總線申請信號;

LHOLDA:占用本地總線應(yīng)答信號;

Wait#:主設(shè)備傳輸暫停信號;

EOT#:數(shù)據(jù)傳輸異常中止信號,用于FIFO溢出或空時中斷數(shù)據(jù)傳輸;

Lint#:用于引起CompaetPCI總線端的中斷信號;

LRST#:本地總線復(fù)位信號;

CCS#:配置寄存器選擇信號。

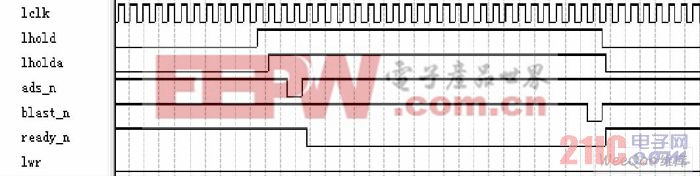

在DMA傳輸過程中主要關(guān)心的信號可簡化為:ADS#、Blast#、LW/R#、Ready#、LHOLD、LHOLDA,如圖3所示。

圖3 PCI局部總線控制時序

圖3中,lclk為本地總線時鐘,當(dāng)PCI9656要發(fā)起一次DMA操作時,先發(fā)送lhold信號申請本地總線,若本地總線空閑則FPGA發(fā)出lholda信號響應(yīng)PCI9656,然后PCI有效ads_n信號以示總線傳輸開始,F(xiàn)PGA使ready_n有效以示總線傳輸正在進行中,此時本地數(shù)據(jù)通過局部數(shù)據(jù)線傳送到PCI總線,或著數(shù)據(jù)由PCI總線傳送到局部邏輯。一次傳輸結(jié)束時PCI使blast_n信號有效并使lhold信號無效,然后FPGA使lholda信號和ready_n信號無效,一次DMA傳輸完成。傳輸中若是DMA讀操作則lwr信號拉低,若為寫操作則拉高。

本地總線位寬為32位,因此本地總線理論速度為264MB·s-1,由于應(yīng)用程序的效率問題和傳輸中一些無效狀態(tài)的存在,目前PCI總線平均速率達到212 MB·s-1,可以滿足目前高速數(shù)據(jù)采集、傳輸對總線傳輸速度的要求。

PCI9656本地總線時序設(shè)計中需要注意blast_n信號有效說明為突發(fā)傳輸最后一個時鐘周期,此時ready_n信號仍然為有效,否則會造成總線等待;在正常讀寫訪問中CCS#信號應(yīng)置高,否則總線訪問將指向配置空間而非內(nèi)存或I/O空間。

5 結(jié)束語

利用PCI9656和FPGA實現(xiàn)了一種高速PCI總線接口,較全面地論述了總線驅(qū)動開發(fā)和局部時序設(shè)計的過程。這種設(shè)計提高了總線傳輸速度,為高速數(shù)據(jù)采集系統(tǒng)的實現(xiàn)創(chuàng)造了條件。

評論