多通道頻率檢測技術的FPGA實現

3 實現方案

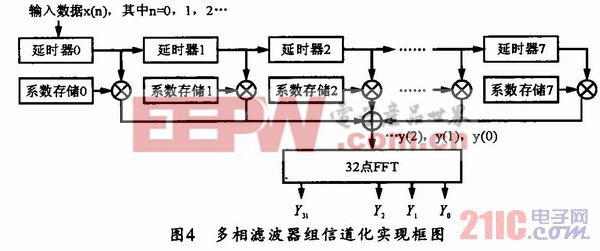

本設計選用的FPGA芯片是Xilinx公司的Virtex-4SX55,該芯片時鐘資源豐富,算術運算單元和專用存儲模塊以及可配置邏輯的使用都很靈活,非常適合當前信號處理系統的功能實現。因此,根據圖2所示的結構,就可以得到一種基于DFT多相濾波器組的信道化解決方案,其具體實現結構如圖4所示。本文引用地址:http://www.104case.com/article/191272.htm

圖4所示結構由延時器、系數存儲器、乘加器和FFT組成。其中延遲器可實現對輸入數據32個周期的延時,存儲器用于存儲濾波器系數。下面對該結構中幾個主要組成模塊的實現及仿真結果進行介紹。

3.1 延時器的實現

本延時器采用FPGA提供的專用存取模塊FIFO來實現32周期延時,其架構體系如圖5所示。圖中,每個延遲單元即是一個FIFO模塊,FIFO的數據輸出特點為先入先出。在本設計中,第一級延遲器的輸出數據將作為下一個延遲器的輸入數據,就相當于第一級FIFO的數據按先進先出的順序依次向第二級FIFO壓入,相鄰兩級的將滿標志與讀使能信號進行握手協議,從而實現數據的延遲輸出。這樣,設計8個同樣結構的FIFO并進行串行級聯,即可滿足該結構的設計要求。

評論