基于TDI-CCD的成像FPGA系統軟件設計應用

2.1 FPGA軟件設計分析

可編程邏輯設計原則的合理應用,為理解FPGA程序設計,實現高效、穩定的數字系統提供了條件。

(1)資源與速率的平衡。資源和速率是FPGA設計的重要指標。通過合理的軟件結構劃分,在高速數據處理區域采用速度優先方法,即通過模塊復用、串/并轉換、數據流水化等方法實現高速數據傳輸;在低速處理區域,采用串行方式和組合邏輯,通過增加扇出實現資源的最優化。

(2)系統與硬件匹配。FPGA內部硬件資源決定設計的結構和方法。采用BLOCK RAM或Distributed RAM,根據數據處理內容、資源利用率要求決定使用方式;另外,利用全局信號線,實現全局變量處理;利用FPGA內部IP和原語實現程序設計,改善程序架構。

(3)同步設計。同步設計是資源與速度的體現,在異步時鐘域數據處理時,采用FIFO轉存,解決同頻異相或異頻問題,實現數據讀取和傳輸。

(4)可靠性設計。軟件設計采用冗余和容錯性設計、簡化設計規模和減少軟件配置項;

2.2 圖像數據處理與分析

2.2.1 數據率和時鐘選擇

CCD圖像輸出數據率計算如下:

式中:F為輸出數據率;Fpixel為CCD像元轉移速率;A為量化等級;Npixel為像元數;Na為啞像元數;TL為行周期。根據指標計算,成像系統的數據率達到1 Gb/s以上,因此,數據傳輸采用10 b數據并行方式,滿足軟硬件設計預定的指標要求。

2.2.2 時鐘域分析

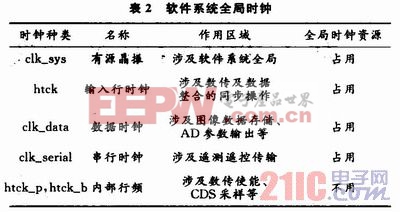

CCD圖像處理單元,主時鐘采用120 MHz有源晶振(elk_sys),通過FPGA內部全局時鐘網絡(BUFG)實現全局走線;設計時不建議使用DCM。系統的主要時鐘如表2所示。本文引用地址:http://www.104case.com/article/191262.htm

系統接收外部行同步時鐘,通過高頻主時鐘同步,并在FPGA內產生內部行頻,用于產生CDS信號及控制邏輯。通過分頻產生串行時鐘,完成遙控遙測信號的收發;產生數據時鐘,完成數據采樣和傳輸;

2.2.3 成像系統軟件結構及功能實現

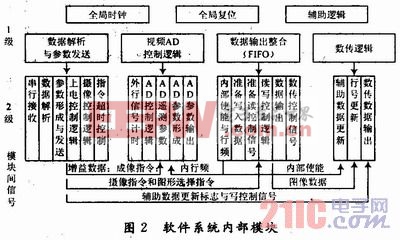

根據軟件系統功能,自頂向下劃分模塊,如圖2所示。為了保證模塊間信號的獨立性,增強了模塊解耦處理,具體的處理原則是:減少模塊IO數量,減少邏輯關聯程度,避免信號控制環路產生;存儲器與后續數據處理操作整合;模塊間避免數據傳輸,減少異步時鐘域的數據同步問題;采用脈沖電平邏輯實現模塊控制等。由于合理劃分了軟件模塊,方便了模塊化設計和仿真驗證,為后續的工作奠定了堅實的基礎。圖2中三級模塊沒有具體給出。

評論