基于FPGA的多路圖像采集系統的軟件設計

用程序實現比較簡單,設置一個地址寄存器sram_addr_reg,將它賦給SRAM的地址控制信號sram_addr。然后在對每一路圖像寫入時,將對應的SRAM的起始地址加上一個固定的基數。如:

本文引用地址:http://www.104case.com/article/191256.htm

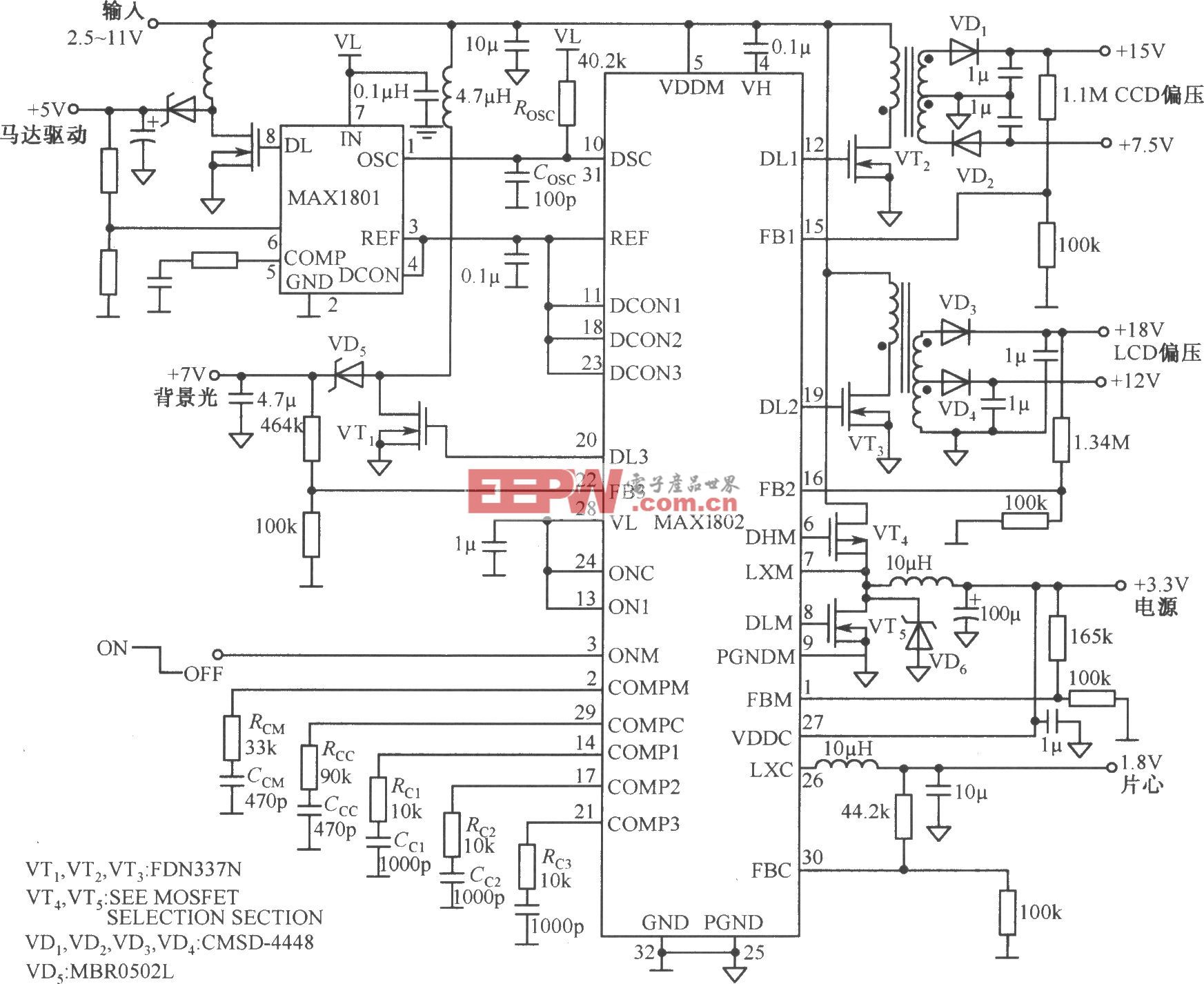

在系統中,LCD屏幕分辨率為640x480,像素時鐘CLK為25MHz,由于FPGA的主時鐘輸入選用了20 MHz的有源時鐘,那么就要求利用Cyclone芯片的內部邏輯資源來實現時鐘倍頻,以產生所需要的CLK(25 MHz)、用Verilog語言編寫參數化的時序生成模塊,產生HSYNC(32 kHz)及VHY-NC(60 Hz)時鐘信號,如圖8所示。

VGA顯示原理與LCD相似,除了在硬件上正確連接ADV7125芯片電路外根據需要的分辨率來生成相應時鐘信號即可。

5 圖像抖動的分析與解決

在系統完成后軟硬件聯調時,出現畫面抖動現象,其中以RTSO為基準而產生乒乓切換的那一路圖像穩定,其他三路都出現不同程度的抖動現象。對此我們做了深入的分析和實驗,分析整個系統的結構可知,系統在多個時鐘控制下共同工作,也就是所說的典型的異步系統。我們知道,數據在異步系統傳輸時對時鐘要求非常嚴格,稍微的一點時鐘偏差都會帶來對有效像素截取的偏差,最終影響圖像的顯示質量。

解決的辦法有兩個,一是加入緩沖機制,利用FIFO對數據存儲的特性來實現數據在異步時鐘之間的無縫傳輸;二是同步時鐘,利用狀態機等方法使得異步系統的時鐘能夠盡可能同步。采用第二種方法對系統進行改進,首先系統中所有的分頻、倍頻盡量使用Quartus 6.0自帶的PLL產生,并且使用專用時鐘引腳進行時鐘輸出;其次把寫時鐘write_clk降為54M,也就是每隔一個像素采集一次。最終,四路圖像都能穩定顯示。

6 結束語

本文實現了一種結合Altera公司生產的CycloneII系列FPGA與視頻解碼芯片ADV7181B的嵌入式圖像采集系統。系統具有低功耗、低成本、高可靠和靈活性好等特點。基于FPGA的多路圖像采集系統采用兩片FPGA作為主控芯片,完成四路視頻畫面的同時顯示和切換,實現兩個FPGA的級聯配置,采用Verilog語言編寫的控制邏輯解決了畫面抖動問題。系統軟件集成度高,硬件結構清晰簡單,即可滿足一般監控場合對多處位置進行實時監控的需求,又能為功能更復雜的圖像處理、壓縮、傳輸系統提供前端圖像數據采集。

評論