基于FPGA高速并行采樣技術的研究

2.2 增益誤差的計算和校正

在本文的設計中,經過模擬前端多相時鐘電路設計,時間相位誤差可以忽略,且ADC的基準電壓由同一電源供電,偏置誤差也可忽略,在此,利用DFT變換校正增益誤差。對于只有增益誤差的第k個子通道的輸出信號yk(n)=gkAcos[2πfin(mn+k)/fs+θ],做N點DFT得:

,因此,經過增益誤差校正輸出信號為:

3 實驗仿真結果

圖5是經過FPGA內部映射之后的時序仿真圖,可以看到經過精心設計的多相時鐘技術以及合理的同步接收使信號的采集效果良好。本文引用地址:http://www.104case.com/article/191253.htm

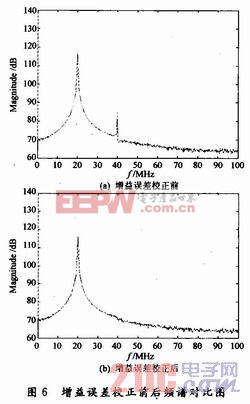

圖6是采集得到的數據經過增益誤差校正前后的頻譜對比圖,可以看到在40 MHz處,雜散得到了明顯的抑制。其中,模擬輸入信號的頻率為20 MHz。

4 結語

針對高速并行ADC時間交叉采樣技術對多相時鐘信號的高要求以及采集數據的誤差,介紹了多相時鐘設計的一種方法和利用FFT技術實現對增益誤差的校正。通過實驗仿真證明,該設計能夠有效提升數據采集系統的性能。

評論