高性能FPGA中的高速SERDES接口

流行的串行協議

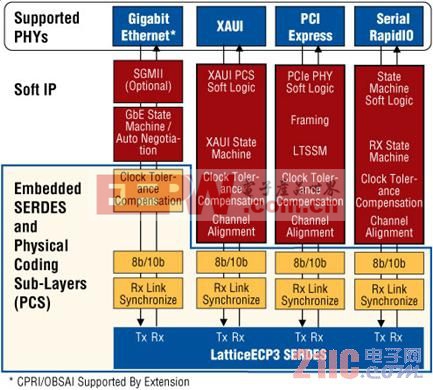

以太網( 1吉比特以太網和10吉比特以太網,或XAUI )和PCI Express是最流行的通信協議。這些協議的每一個都從并行總線接口發展成串行接口,以跟上日益增加的數據傳輸速率。這些流行的協議共享物理編碼子層中的公共塊。例如,它們都使用8b/10b編碼。 8b/10b編碼提供了非常好的直流平衡,最多5個全0或全1并有良好的跳變密度。這些都有助于提高傳輸的可靠性。如圖2所示,在萊迪思的ECP2M和ECP3器件中的嵌入式ASIC模塊包含了PMA和PMD以及PCS公共塊,例如,鏈接同步塊和8b/10b編碼器/解碼器。

圖2 LatticeECP3支持流行的串行協議

Ethernet

以太網是使用最廣泛的通信協議。以太網的數據傳輸速率已經從10 Mbps發展至100 Mbps,又發展至1吉比特( 1000 Mbps ),繼而又發展多吉比特范圍: 10 Gbps 、 40 Gbps和100 Gbps。隨著數據傳輸率的發展,鏈路已經從并行接口(MII、 GMII )發展到串行鏈路(GE、SGMII 、 XAUI等) 。

LatticeECP3系列完全符合吉比特以太網和10吉比特以太網協議。該SERDES是符合針對1000 BASE-X吉比特以太網的IEEE 802.3z規范和針對10吉比特以太網XAUI 的IEEE 802.3-2005規范。如圖2所示,LatticeECP3器件支持嵌入SERDES和其他塊的以太網物理層,如鏈路同步、在器件中8b/10b編碼/解碼以及時鐘容限補償的ASIC模塊。將萊迪思的GE/ SGMII PCS和MAC IP組合在一起時 ,LatticeECP3為用戶提供了一個完全集成的、完全兼容吉比特以太網的解決方案。

LatticeECP3 SERDES超過了由IEEE 802.3-2005規范針對XAUI定義的抖動規格。萊迪思的XAUI IP和10吉比特以太網MAC IP內核提供一個完全集成的,完全符合10吉比特以太網的平臺。LatticeECP3是完全符合支持1吉比特和10吉比特以太網的業界最低成本的FPGA.

PCI Express

PCI Express是下一代外圍組件互連( PCI )標準。該PCI Express協議是為了解決日益增加的帶寬需求,通過電纜或針對擴展卡的連接器插槽、提供一個可升級的、芯片之間點對點的串行連接,同時保持與傳統的PCI在軟件層相兼容。

單個PCI Express串行鏈路是雙單工連接,規定每個鏈路為2.5Gbps的速率(5Gbps或更高的速率,針對2.0版和以后的規范),可以構成x1、x2、x4、x8 , x12 , x16和x32鏈路寬度,以實現更大的帶寬。串行實現是便宜的,可以進一步推動延伸長度、減輕共模噪聲、關注現有源同步并行接口(如常規的PCI )的相偏 ,并減少需要連接通道的總數。LatticeECP3 SERDES完全符合PCI Express 1.1版的抖動規范。與萊迪思的PCI Express端點控制器IP相結合 ,為設計人員提供了一種低成本的PCI Express平臺。

評論