第二代串行 RapidIO 和低成本、低功耗的 FPGA

低成本、低功耗擁有SRIO功能的FPGA的作用和優勢

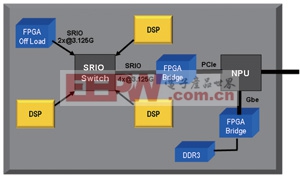

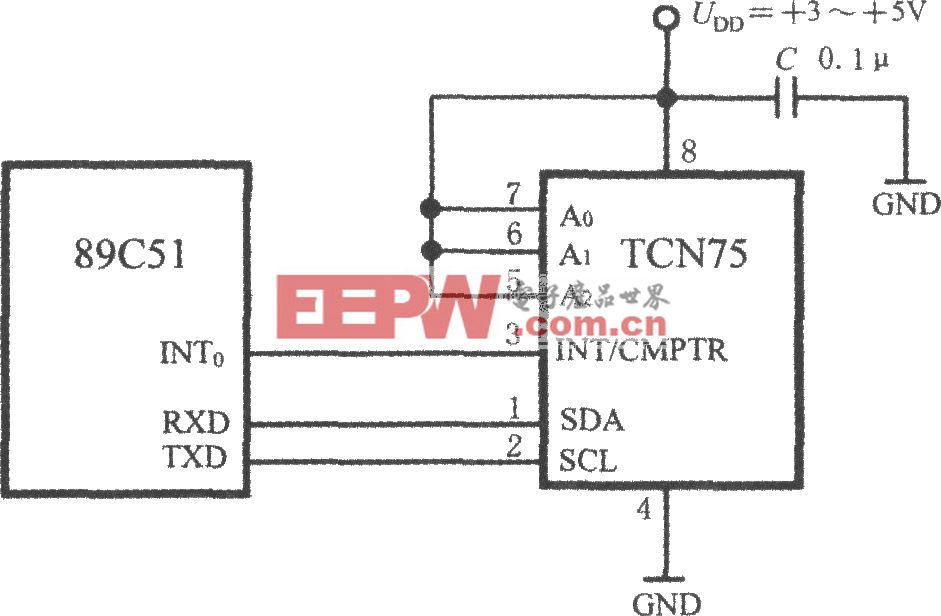

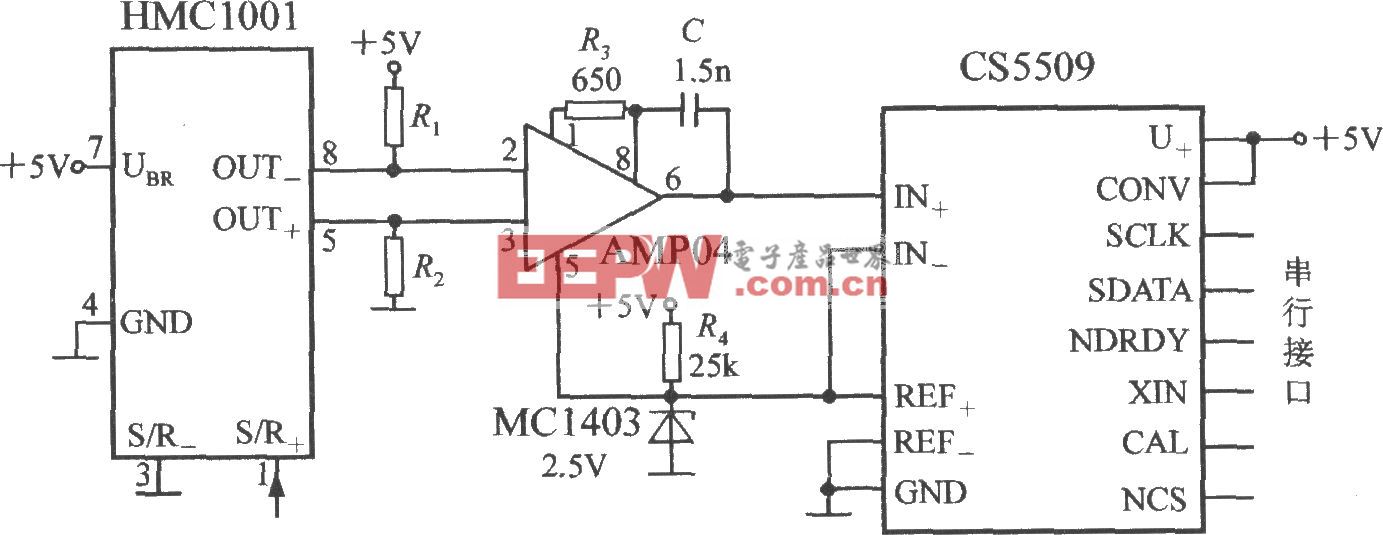

如上所述,許多處理都由于DSP和NPU而失敗,而通常情況下,它們兩者的分工不同。DSP應用,盡管也進行密集型處理,但往往需要更多的中斷驅動(如門鈴),因為它們是在處理陣列中實現的,或者要接口到一個SRIO開關或終端——可能甚至要提供從SRIO到另一個基于SERDES的協議,如GbE或PCIe的橋接機制。而NPU更多地扮演了一個警察的角色來進行數據處理,主要負責通信量和隊列處理。如圖3中的示例所示,說明了低成本、低功耗FPGA可以如何協助實現一個成功且有效的系統解決方案。

圖3 FPGA應用示例

FPGA因其固有的靈活性和快速的產品上市時間的優勢,超越了ASIC而長期受到市場歡迎,但是最近,這些優勢只能通過使用高級的高端器件才能實現,這就提高了成本和功耗預算。之前,低成本、低功耗FPGA僅限于“接口邏輯”和“錯誤修正”應用。然而,隨著FPGA的價值定位大大地擴展,現在已不再是如此。為了支持處理需求,保持嚴格的成本和功耗預算,FPGA的架構已經經歷了發展變化,顯著地提高了性能、特性和邏輯密度,并且以比傳統FPGA更低的功耗和價格來實現。增強的功能,如集成的SERDES、高速嵌入式DSP塊、DDR3存儲器支持和嵌入式存儲器功能,已成為處理設計中的關鍵組成部分。系統工程師和設計工程師現在能夠利用這些可編程平臺實現復雜的信號路徑應用,支持RRH和基帶處理功能,以及有線和圖像處理應用,并且與傳統、高端的帶有SERDES功能的FPGA產品相比,具有更低的功耗和成本。

小結

系統設計人員將繼續面臨設計更高性能系統并同時保持較低的系統構建和運營成本的壓力。而這種壓力還將繼續延續下去。

過去,FPGA在系統設計中發揮了重要作用,但現在還需要新的性能,同時需要降低整個系統的構建和運營成本。功能豐富、低成本的FPGA實現了快速的產品上市時間與較短的投資回報周期,并且擁有能夠適應不斷發展的標準的靈活性和性能。系統/設計工程師現在還擁有了一個令人興奮的、改進的工具集來解決不斷演進的信號處理市場的挑戰。

評論