基于MAX6675多路溫度采集系統設計與實現

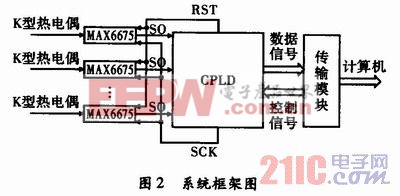

2 系統構架

系統框架如圖2所示,該系統以CPLD為核心,由多路K型熱電偶和MAX6675將外界溫度模擬信號采集并轉換成數字信號,并將數據傳入CPLD進行相應的處理,然后通過通信模塊將數據傳送給計算機,最后用計算機做數據統計及處理。系統中的通信模塊可以根據工程或實驗環境的不同使用不同通信方法,如串口通信、PCI傳輸卡等。由于工程應用的原因,本文使用PCI傳輸卡作為數據傳輸方式。本文引用地址:http://www.104case.com/article/191151.htm

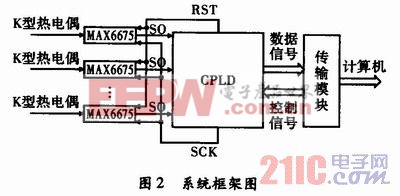

3 CPLD內部邏輯

如圖2所示,K型熱電偶將采集的模擬信號傳送給MAX6675,再由它轉化成數字信號傳入CPLD,CPLD根據MAX6675芯片的時序進行數據處理得到需要的信號,最后由傳輸模塊傳到計算機進行數據顯示和統計、處理。所以本文的重點工作便在CPLD內部邏輯的設計。在進行內部邏輯設計之前,須了解MAX6675的工作時序與原理:當CS引腳由高電平變為低電平時,MAX6675停止任何信號的轉換,并在時鐘SCK的作用下向外輸出已轉換的數據;當CS引腳從低電平變到高電平時,MAX6675將進行下一輪數據的轉換。一個完整的數據讀取需要16個時鐘周期,數據的讀取在SCK的下降沿進行。MAX6675的工作時序圖如圖3所示。

如圖3所示,根據芯片手冊tcss是CS下降到SCK上升的時間,規定其最小值為100 ns,tCH+tCL為SCK的一個時鐘周期,規定最小周期為200 ns,tDV為CS下降沿到數據輸出的時間,規定最大不超過100 ns。tDO為SCK下降到輸出有效數據的時間,tTR為CS上升沿到數據停止輸出地時間,規定最大值均為100 ns。根據這些手冊上的這些時間規定,在設計CPLD內部邏輯電路時便嚴格按照要求,將SCK時鐘周期設為1 000 ns即1 MHz,tcss設為1 000 ns,tDVtTR都設為100ns。圖中還可以看出SO是16位的輸出數據,其中只有D14~D3位為溫度數據,D15位為無用位,D2位為熱電偶斷線測試位,D1位為MAX6675標識符,D0位為三態,所以從16位數據中取出D14~D3這12位數據進行轉換和處理。基于以上分析,設計了如圖4所示的內部邏輯模塊。

模數轉換器相關文章:模數轉換器工作原理

熱電偶相關文章:熱電偶原理

評論