一種基于AT25T1024 FLASH的高速SPI接口設計

從設備選擇寄存器的SS位置“1”時,表示選中從設備。置“0”表示不選擇任何從設備,本設計僅支持一個從設備。

加載配置數據起始寄存器的SPICFGSTART位置“1”時,配置數據自動從FLASH中讀取并寫入到DPRAM中,置“0”不進行讀FLASH操作。

加載配置數據完成寄存器為只讀寄存器,用來判斷數據是否已經加載完成。

2.5 SPI緩沖區設計

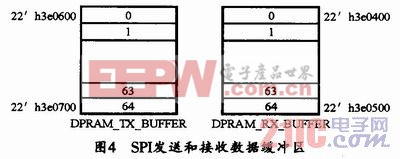

圖4所示為主機可直接訪問的SPI接口內部DPRAM發送和接收數據緩沖區。本文引用地址:http://www.104case.com/article/191112.htm

SPI發送數據緩沖區深度65,數據位寬32位,其中地址22’h 3e0600存放訪問AT25F1024存儲器的指令,當進行寫操作時,從數據發送緩沖區最低位地址22’h3e0604開始,將數據搬運出來,串行發送到AT25F1024存儲器。

SPI接收數據緩沖區深度65,數據位寬32位,其中地址22’h3e0400緩存讀取的AT25F1024配置和狀態信息,偏移地址22’h3e0404~22’ h3e0500緩存指定FLASH讀取的總線配置數據數據,最大緩存2048位。

3 數據搬運時間

3.1 主機寫片外FLASH的時間

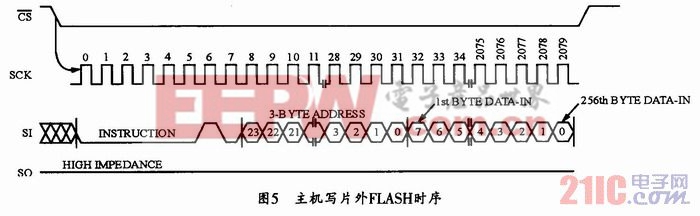

本設計使用的存儲器AT25F1024緩沖數據寄存器大小2048位,寫使能需要8個串行時鐘周期,向片外FLASH傳輸2048位數據需要2080個串行時鐘周期(包括了32位寫指令的傳輸數據),這樣寫一次需要時間為2088個時鐘周期,主機將1Mbits的FLASH填滿,時間大約為2088 x50ns(串行時鐘40/2MHz)×512 (填滿1Mbits需要512次寫操作)=53.4ms。讀1Mbits的FLASH需要的時間約為2080x50x512=53.2ms。圖5所示為主機寫片外FLASH時序圖。

3.2 讀取數據并加載到片內DPRAM的時間

通過SO管腳讀取AT25F1024的過程按下面順序執行,當片選拉低選擇此器件之后,通過SI線發送讀指令,后面跟隨要讀的地址(三個字節地址),指令傳輸完之后,SI線上的任何數據將被忽略。指定地址的數據接著被移出到SO線上。如果僅讀取一個字節,當數據讀出來之后,CS信號驅動為高。讀指令繼續時,字節地址自動增加,并且數據不斷被搬運出來。

AT25F1024緩沖數據寄存器大小2048位,在本設計中,寫使能需要32個串行時鐘周期,這樣讀取一次需要時間為2080個時鐘周期,將片內DPRAM(DPRAM大小14940字節)填滿,時間大約為2080x50ns(串行時鐘40/2MHZ)x59(填滿片內DPRAM需要大約59次讀操作)=6.13ms。

4 結束語

本文從應用的實際需求出發,在FPGA中實現了對外部FLASH進行讀寫的高速SPI接口,并已在某型板卡中成功應用。本文重點用有限狀態機的形式對各部分的工作原理和實現方法進行了描述。在FPGA資源比較緊張,限制管腳的使用數目,對速率又有比較高的需求的情況下,利用此SPI接口進行數據的加載或者固化,具有很高的應用價值。

評論