基于FPGA的超聲波信號處理研究

2 FIR濾波器的FPGA實現

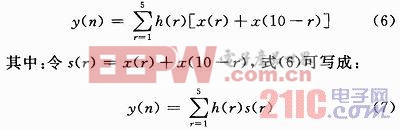

由式(4)可知,FIR濾波器的數學表達式就是卷積運算,也就是做乘加運算。例如,一個M階的FIR濾波器的輸出是輸入樣本的M個依次值的加權和,加權系數就是此濾波器的單位沖激響應值。對于上節設計的10階線性FIR濾波器,可以得到:

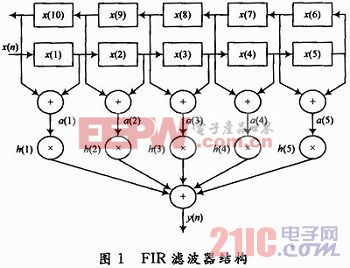

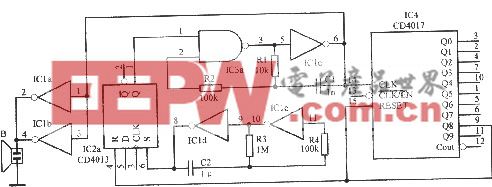

這樣,10階FIR濾波器的結構可以描述為:輸入樣本x(n)經過10階移位寄存器延遲后得到10個具有不同延遲的抽頭,將對稱的抽頭值相加后再與相應的權系數相乘,5個乘積相加就得到濾波器的輸出值。濾波器結構如圖1所示。本文引用地址:http://www.104case.com/article/191079.htm

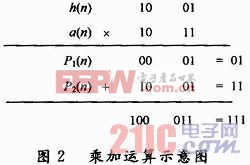

濾波器抽頭與權系數之間存在著乘法運算,在硬件實現中乘法運算是相當復雜的運算,不僅占用大量硬件資源,而且運算速度較慢。為了提高運算速度,在此利用FPGA邏輯單元(LE)中的查找表實現替代乘法運算的查表運算。為了說明方便,在此以4階濾波器為例,數據為2位的二進制整形。設a(1)=01,a(2)=11,h(1)=10,h(2)=01,權系數與抽頭之間的乘加運算如圖2所示。

圖2中,P1(n)為抽頭低位與權系數的乘積結果,P2(n)為抽頭高位與權系數的乘積結果,在此稱之為單位積。常規的計算順序是先將P1(n)和P2(n)的對應項在垂直方向上移位相加,所得結果再進行水平方向上相加。但是從圖中可以看出,先將P1(n)和P2(n)在水平方向上相加,然后再進行垂直方向上移位相加,所得的結果是一樣的。第二種順序中,P1(n)和P2(n)是h(n)和a(n)的某個比特位的乘積,而對于設計好的FIR濾波器h(n)是固定的,這樣就可以通過a(n)某比特位的組合來查表求出P1(n)或P2(n),并在水平方向上實現求和。如表1所示,a1(n)表示a(n)的低位組合,單位積P1表示相應的權系數和。

評論