基于FPGA短波差分跳頻信號發生器的設計與實現

摘要:差分跳頻(DFH)是一種新的短波跳頻技術,它主要歸結為一種G函數算法,這種G函數集跳頻圖案、信息調制與解調于一體。它的通信機理與常規跳頻完全不同,較好的解決了數據速率和跟蹤、干擾等問題,代表了當前短波通信的一個重要發展方向。鑒于此,在研究G函數算法原理的基礎之上,重點對短波差分跳頻信號的發生器進行基于FPGA的整體優化設計,并在軟件和硬件環境下進行仿真與實現,從而指導工程實踐。

關鍵詞:差分跳頻;G函數;現場可編程門陣列

0 引言

短波通信具有通信距離遠、機動靈活、成本低廉等優點,而且是一種抗毀性較強的通信方式,因此在多種領域得到了廣泛的應用。隨著跳頻和自適應等新技術的發展,短波通信的性能也得到進一步的提高。但由于短波信道的特點,一方面,其存在多普勒頻移和多徑效應,嚴重影響短波通信的系統性能,特別是對于短波數據傳輸系統,往往達不到較高傳輸速率;另一方面,其頻率資源有限,易受干擾和竊聽,再加上短波通信所使用的媒介,造成短波通信是一個時變、衰落信道,保持良好的通信效果有較高難度。美國Sanders公司推出一種相關跳頻電臺采用的差分跳頻技術在短波信道上實現了跳速為5000hop/s,傳輸速率最低為2400bps,最高可達19200bps的指標,這在傳統的跳頻系統中是很難實現的。采用差分跳頻技術不僅改變了短波電臺由于信道帶寬窄、空中信道時變多徑特性而導致的低速率數據傳輸的局面,而且極大地提高了抗跟蹤干擾的能力,代表了新一代短波通信技術的發展方向。考慮到使用FPGA器件進行數字系統設計,不僅可以簡化設計過程,而且可以降低整個系統的體積和成本,增加系統的可靠性,本文對短波差分跳頻信號的發生器進行基于FPGA的整體設計。

1 G函數算法原理

差分跳頻系統的關鍵技術在于G函數的實現。差分跳頻G函數的特點是利用跳頻頻率的相關性來攜帶待發送的數據信息,同時所產生的頻率序列具有良好的隨機性和均勻性。常規的G函數表達式為:

![]()

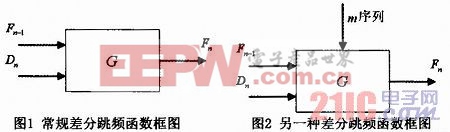

式(1)是利用前后跳頻Fn,Fn-1之間的相關性來攜帶數據信息Dn,如圖1所示。另一種G函數算法是由前一跳的頻率、m序列和數據信息Dn來決定當前的頻率值Fn,如圖2所示,其數學表達式為:

![]()

G是一個特定的函數,由它決定差分跳頻的算法。由此可見,m序列控制的G函數算法在相鄰跳變頻率之間通過數據序列建立了一定的相關性,亦即相鄰頻率的相關性攜帶了待發送的數據信息,Dn可取1~4bits。

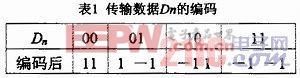

例如,當傳輸的數據信息Dn取2bits時,對Dn編碼見表1。

評論