基于FPGA的FIR數字濾波器的優化設計

4.4 FPGA實現與仿真

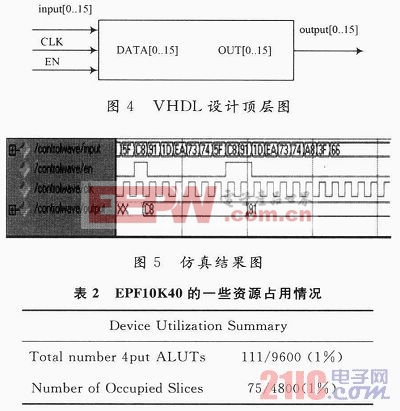

參照圖3中給出的設計流程,使用VHDL語言實現了該常系數濾波器的行為描述,圖4是濾波器的實現頂層圖。FPGA采用AItera公司的EPF 10K40芯片,該芯片最高的單路運行速率為200 MHz。圖5是在Max+PIusⅡ中的仿真結果。表2給出了EPF10K40的一些資源占用情況。本文引用地址:http://www.104case.com/article/191069.htm

5 基于FPGA的FIR試驗結果

為驗證本文提出的算法的普遍性,以并行DA和2C編碼方式設計了一系列階數從16到256階的FIR濾波器,濾波器在Altera公司的開發軟件Max+PlusⅡ中進行編譯和布局布線,采用的目標器件為EPF10K40芯片,在系統中對3種實現結構進行測試,測試數據位寬為8位。通過表3的比較結果可以看出,使用CSD編碼,資源耗用明顯下降。當FIR階數很高,系數很復雜時,CSD編碼的優勢會更加顯著。表4給出了N=64時DA算法和CSD算法的具體性能指標,從結果來看,CSD編碼相對于單純的DA在系統資源和整個系統延遲上有明顯的提高。

6 結語

濾波器用VHDL硬件描述語言實現,采用Altera公司的EPF10K40芯片,在Max+PlusⅡ中進行了仿真驗證。從結果來看,文中所提出的CSD編碼算法,具有一定的研究價值和實用價值,CSD編碼在處理序列較多的情況下,在資源占用、速度處理方面的效果尤為明顯。采用CSD編碼方式對FIR濾波器進行優化設計,可減少FIR實現的FPGA資源消耗。

評論