基于FPGA的通用異步收發器設計

摘要:采用Verilog HDL語言作為硬件功能的描述,運用模塊化設計方法分別設計了通用異步收發器(UART)的發送模塊、接收模塊和波特率發生器,并結合現場可編程門陣列(FPGA)的特點,實現了一個可移植的UART模塊。該設計不僅實現了串行異步通信的主要功能,而且電路簡單,工作穩定、可靠,可以將其靈活地嵌入到各個通信系統中。

關鍵詞:通用異步收發器;現場可編程門陣列;Verilog HDL;串行通信

串行通信要求的傳輸線少,可靠性高,傳輸距離遠,被廣泛應用于計算機和外設的數據交換。通常都由通用異步收發器(UART)來實現串口通信的功能。在實際應用中,往往只需要UART的幾個主要功能,專用的接口芯片會造成資源浪費和成本提高。隨著FPGA/CPLD的飛速發展與其在現代電子設計中的廣泛應用,FPGA/CPLD功能強大、開發過程投資小、周期短、可反復編程、保密性好等特點也越來越明顯。因此可以充分利用其資源,在芯片上集成UART功能模塊,從而簡化了電路、縮小了體積、提高了可靠性,而且設計時的靈活性更大,周期更短。鑒于此本文提出了一種采用FPGA實現UART功能的方法,可以有效地解決上述問題。

1 UART的工作原理

UART(Universal Asynchronous Receiver Transmitter,通用異步收發器)是廣泛使用的異步串行數據傳輸協議。在串行通信中,數據以字節為單位的字節幀進行傳送。發送端和接收端必須按照相同的字節幀格式和波特率進行通信。UART控制器所傳輸的一幀串行數據包括1位起始位(低電平)、5~8位數據位、1位校驗位(可選)和停止位(可為1,1.5,2位)。起始位是字節幀的開始,使數據線處于邏輯0狀態,用于向接收端表明開始發送數據幀,起到使發送和接收設備實現同步的功能。停止位是字節幀的終止,使數據線處于邏輯1狀態。用于向接收端表明數據幀發送完畢。波特率采用標準速率9 600 b/s。數據在傳輸時,低位在前,高位在后。接收端檢測并確認起始位后,接收數據位。停止

位接收完畢后,向CPU發出中斷信號,同時將數據發送到計算機的8位數據總線上;發送數據時,先由CPU設置波特率,然后將8位并行數據加上起始位和停止位發送給外設。停止位發送完畢后,向CPU發出中斷信號。在數據發送和接收過程中,CPU可以通過控制信號來讀取UART的工作狀態,以便進行實時處理。

2 UART的模塊化設計

2.1 系統總體結構

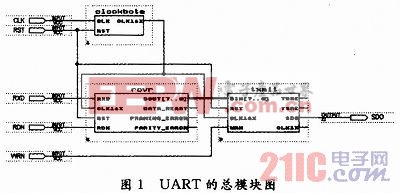

在大規模電路的設計中,廣泛采用層次化、結構化的設計方法。它將一個完整的硬件設計任務從系統級開始,劃分為若干個可操作的模塊,編制出相應的模型并進行仿真驗證,最后在系統級上進行組合。這樣在提高設計效率的同時又提高了設計質量,是目前復雜數字系統實現的主要手段,也是本文設計思想的基礎。按照系統功能進行劃分,UART主要由波特率發生器、接收模塊和發送模塊三大部分組成。在Maxp-lusⅡ仿真環境下,由各個子模塊進行綜合的系統總模塊如圖1所示。下面分別討論發送模塊、接收模塊和波特率發生器模塊的具體實現過程。

評論