基于FPGA的高速自適應濾波器的實現

現代通信信號處理發展到3G、4G時代后,每秒上百兆比特處理速度的要求對于自適應處理技術是一個極大的挑戰。使用具有高度并行結構的FPGA實現自適應算法以及完成相應的調整和優化,相比于在DSP芯片上的算法實現可以達到更高的運行速度。本文分析了自適應LMS算法及其在FPGA上的實現,并進行算法結構的改進優化,利用DSP Builder在Altera DE2-70平臺的FPGA芯片上實現相應自適應算法并下載到目標板上進行板級測試。

1 自適應LMS算法[1-2]

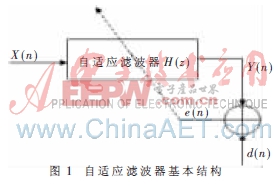

自適應濾波器的特點在于濾波器參數可以自動地根據某種準則調整到相應的最優濾波情況。其基本框圖如圖1所示。

圖中,X(n)為輸入信號,y(n)為濾波信號,d(n)為期望信號,e(n)為誤差信號,用來調整自適應濾波權系數。自適應濾波函數H(z)的濾波參系數是通過一定的自適應算法,根據誤差信號e(n)進行自動調整,目的是使得誤差e(n)的模值越來越小。

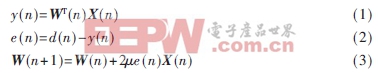

自適應LMS算法表述如下:

2 算法的仿真和FPGA實現

本設計使用的工具DSP Builder是Altera公司推出的基于Altera FPGA芯片的系統級(算法級)設計工具,它架構在多個軟件工具之上,并把系統級和RTL級兩個設計領域的設計工具連接起來,最大程度地發揮了兩種工具的優勢[3]。它依賴于Matlab/Simulink進行建模和仿真,可以把建模設計文件轉換為硬件描述語言文件。

考慮橫向LMS算法的FPGA實現時,有兩種拓撲結構可以選擇。一種是直接型FIR結構,另一種是轉置型FIR結構。從算法效果上來說,這兩種結構是一致的,但是轉置型結構的濾波部分的關鍵路徑會更短,能夠綜合出更高主頻的電路[4]。故在Simulink中利用DSP Builder采用轉置型LMS結構(Transpose Form-LMS)進行建模,模型參數為8階16位定點格式。

對于收斂步長因子的選取采用二進制移位的方式,只改變數據的連線,不會增加系統資源消耗和計算時間消耗。這里將迭代處理部分左移動10位,即收斂步長因子為2-10,約為0.001。Simulink中,仿真信號為模值等于1的正弦波疊加方差為0.01的高斯白噪聲,建立自適應噪聲對消模型,濾波情況如圖2所示。

利用Signal Compiler工具將模型轉換成硬件描述語言。用Quartus對轉換后的HDL進行綜合、布線布局,得到52.02 MHz(19.223 ns)的系統頻率表現。對EP2C70-F896C6芯片上單個乘法器進行測試,得到一個乘法運算需要的時間滯后為13.8 ns。考慮上面的LMS算法,一次迭代過程至少消耗28 ns以上的時間。這說明,該LMS系統只能運行在35.7 MHz(28 ns)以下。如果頻率超過35.7 MHz,雖不會造成器件時序違規,但在運行時序上就不會滿足標準LMS算法。

3 算法的改進和FPGA實現

3.1 馳豫超前流水線優化

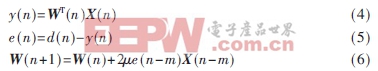

通過馳豫超前流水線技術改進的TFLMS算法稱為TFDLMS(TF-Delay-LMS)算法,改進的算法結構如下[4]:

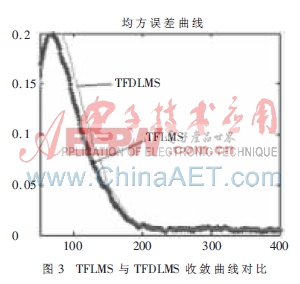

改進結構的特點是,在式(6)權系數更新中,誤差與輸入都不使用當前時刻的數據,而是采用過去的數據來馳豫近似計算。式(5)和式(6)在這種情況下可以同時進行流水計算,斬斷了原先串行的關鍵路徑,提高了效率。對馳豫寄存器m的個數需要合理的選取,若m太大,則對原系統影響較大;若太小則不易后續時序重構的優化,這里取m=4進行Matlab仿真。仿真結果如圖3所示。

如圖3所示,TFDLMS算法在收斂初期由于誤差e隨著濾波的進行改變一般比較大,所以在收斂過程中的性能會稍次于TFLMS算法。在穩態的時候,由于誤差e在此刻一般比較小,所以近似手段對穩態的影響會比較小。考慮到改進后TFDLMS的高度并行的處理結構,在收斂以及穩態表現上的微小影響的代價是值得的。

在Simulink中建模,將TFDLMS模型轉換為HDL,在Quartus中綜合布線布局,得到122.79 MHz的頻率表現。由于TFDLMS采用馳豫流水計算,已經是近似計算,因此無需考慮標準LMS算法的嚴格串行計算時間問題,此時的系統工作頻率可以認為是采樣吞吐頻率。顯然,改進后的算法結構系統吞吐頻率有很大的提高。

3.2 時序重構優化

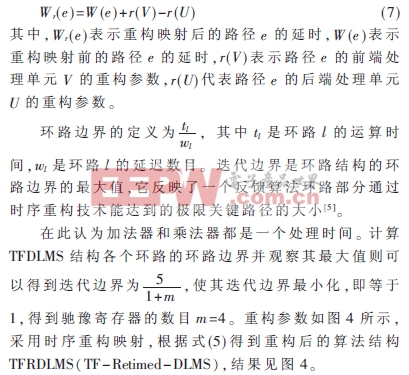

時序重構又稱重定時(Retiming),是一種在保持系統功能不變的前提下改變系統延遲數目和分布的方法[5]。時序重構的映射等式定義為:

評論