基于FPGA的高速數據采集系統設計

摘要:為了在提高數據采集卡的速度的同時降低成本,設計了一種應用流水線存儲技術的數據采集系統。該系統應用軟件與硬件相結合的方式來控制實現,通過MAX1308模數轉換器完成ADC的轉化過程,采用多片Nandflash流水線數據存儲模式對高速采集的數據進行存儲。搭建硬件電路,并在FPGA內部通過編寫VHDL語言實現了采集模塊、控制與存儲模塊和Nandflash存儲功能。調試結果表明,芯片的讀寫時序信號對應的位置準確無誤,沒有出現時序混亂,且采集速度能保持在10 Mh/s以上。系統實現了低成本、高速多路采集的設計要求。

關鍵詞:高速采集;流水線存儲;FPGA

0 引言

為使計算機能對數據采集系統輸入的模擬量進行處理,必須經由數據采集系統將模擬量轉化為數字量。FPGA是在CPLD等邏輯器件的基礎上發展起來的,其高集成度能大大縮小電路板的尺寸,降低系統成本,提高系統的性能和可靠性,適合于時序、組合等邏輯電路的應用場合。一個完整成型的探測系統通常都有采集儲存部分,無論是電信號、光信號、聲音信號等在被探測器接收到后,大部分都需要轉化為數字信號才能再傳給處理器完成分析、判斷的過程。現在的一些高速大容量采集系統,往往價格比較昂貴。本論文主要論述一種應用FPGA等來控制,采用多片Nandflash存儲的低成本、高速、多路、可靠的數據采集系統,本文主要探討硬件設計和存儲設計。

1 系統總體設計方案

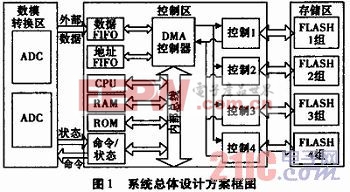

數據采集系統的工作原理是:各種信息經過傳感器后轉化成模擬電量信號,通過ADC將模擬量轉換為數字量信號,而后進行傳輸存儲和處理。本系統中,在軟件和硬件相結合的控制下,系統將采集到的模擬信號經過A/D轉換器件轉換后,將轉換結果先緩存到FIFO,再轉存到非易失性Nandtlash陣列中。其中,FIFO不但可以實現緩存功能,還可以解決A/D轉換之后數據位數跟Nandflash存儲器的數據線位數不匹配的矛盾。如圖1系統總體設計方案框圖所示,本系統采用FPGA內部軟核microblaze處理器作主控制器即軟件控制器,而FPGA內部邏輯資源則用于產生硬件控制時序,整個系統就是在兩者相結合協調下進行數據的采集以及傳輸。

評論