基于FPGA的原型能為您做些什么

基于FPGA的原型可滿足不同目的需求

原型設計不是一個按幾個按鈕就能完成的過程,在它不同的階段需要仔細的關注和思考。除說明這個過程需要完成的工作和涉及到的專業知識外,我們還應解釋在 SoC 項目中該進行(或者不該進行)原型設計的原因。

在與原型設計人員多年交談中,我們最常問到的一個問題是“為什么您這么做?”答案有多種多樣,我們把它們總結成了表1中幾條常見的理由。系統了解這些項目的目的和我們進行原型設計的原因,將有助于我們判斷基于FPGA的原型設計是否能為我們的下一個項目提供幫助。

因此,讓我們探究一下表1所述的目的以及基于FPGA的原型方法如何能幫助實現這些目的。

高性能與準確度

只有基于FPGA的原型才能提供正確測試設計各個方面所需的速度和準確度。我們把這個理由放在首位的原因是,雖然項目有許多需要實現的給定目的,但對需要進行原型設計的團隊來說,這可能是所有理由中最根本的原因。舉例來說,這個團隊的目的可能是驗證某些SoC的嵌入式軟件,觀察其在真實硬件上全速運行的情況,但使用原型的根本原因是為了確保高性能與準確度。我們在虛擬系統中可以在更高的性能水平下驗證該軟件,但我們無法達到使用真實的RTL所能實現的準確度。

實時數據流

難以驗證SoC的原因之一是因為其狀態取決于許多變量,包括其之前的狀態、輸入的次序以及更廣泛的SoC輸出系統效應(以及可能的反饋)。將SoC設計與系統的其他部分相連并以實時速度運行,可以讓我們立即觀察到實時條件、輸入和系統反饋的變化帶來的效應。

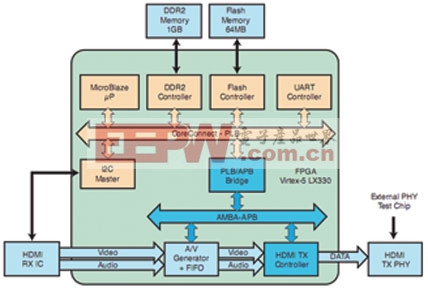

葡萄牙波爾圖市Synopsys公司IP團隊開發的HDMI原型中的實時數據流就是一個很好的例子。在本例中,高清(HD)媒體數據流經處理內核的原型輸出到高清顯示器上,如圖1的方框圖所示。

圖1 HDMI 原型方框圖

通過使用投片前的原型,我們可以立即看到和聽到不同的高清數據在我們的設計上的效果,反之亦然。只有采用基于FPGA的原型方法才支持這種實時數據流,不僅給此類多媒體應用帶來極大好處,也能給許多其他要求對輸入數據流做出實時響應的應用帶來諸多裨益。

軟硬件集成

在上述實例中,讀者可能已經注意到原型使用了一塊小型MicroBlazeTM CPU,并備有外設和存儲器,從而體現了一個 SoC的所有常見模塊。在這個設計中,運行在CPU上的軟件主要用于加載和控制A/V處理。然而,在許多SoC設計中,軟件最耗精力。

鑒于軟件已成為SoC開發工作的主體部分,軟件工作在項目日程中占據關鍵位置越來越常見。當SoC能夠有效達到量產標準的時候,決定項目實際完成日期的是軟件開發和驗證工作。在這種情況下,系統開發團隊如何才能提升軟件開發和驗證工作的效率呢?要回答這個問題,我們需要查看軟件開發團隊把時間都花在什么地方。

為軟件開發建立SoC的模型

軟件由于自身的復雜性,很難做到完美。對我們在日常使用計算機的過程中遇到的軟件升級、服務包和漏洞修補的情況,我們都已經司空見慣。但是,具體到嵌入 SoC 中的軟件,這種無休止的軟件改進方法就遇到了障礙。另一方面,相比于通用的計算機軟件而言,與嵌入式軟件互動的系統,其設定的使用模式和環境條件都更容易確定。而且,為較簡單的系統開發的嵌入式軟件可以比較簡單,也就更易于全面驗證。舉例來說,控制車輛子系統或電子玩具的SoC比在實時操作系統(RTOS)上運行許多應用和流程的智能手機更容易進行全面測試。

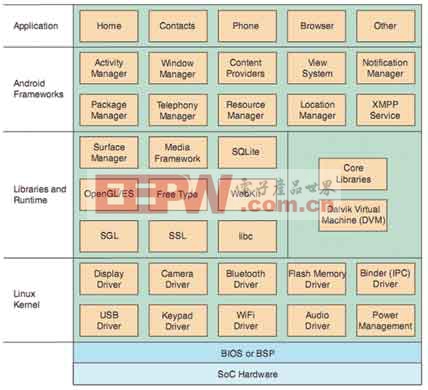

如果我們更加仔細地觀察運行在這類智能手機上的軟件,例如圖2所示的Android軟件,我們可以看到一種多層布置,這稱為軟件協議棧。

圖2 Android軟件協議棧

在觀察軟件協議棧時,我們會發現,協議棧的最底層——也就是那些最接近硬件的部分,主要是為了滿足將軟件映射到SoC硬件上的需求。這就需要對硬件有絕對的了解,甚至包括地址和時鐘周期等。軟件協議棧最底層的設計人員往往稱自己為平臺工程師,他們的工作就是準確描述硬件,以便協議棧的更高層次能夠識別和重復使用。這種描述被某些 RTOS廠商稱為板支持包(BSP),與我們日常使用的 PC 的基本輸入/輸出系統(BIOS)類似。

協議棧從下往上第二層包含 RTOS的內核以及將較高層次的軟件與被描述的硬件相連的必要驅動程序。在這些協議棧的最底層中,平臺工程師和驅動程序開發人員需要在真實的SoC或完全準確的SoC模型上驗證他們的代碼。這個層面的軟件開發人員需要全面了解各時鐘周期軟件的行為。

作為軟件開發人員的另一極,在協議棧的頂層,我們可以看到用戶空間,在這里可以同時運行多個應用,比如像智能電話中的聯系人管理器、視頻顯示器、互聯網瀏覽器和實際呼叫的電話子系統。這些應用中的每一個都不能直接訪問SoC硬件,而且實際上在某種程度上違背了所有硬件考慮事項。這些應用依賴運行在協議棧較低層的軟件代表自己與SoC硬件及系統其他部分通信。

我們可以歸納為:在協議棧的每一層,軟件開發人員只需要一個足夠準確的模型來讓自己的代碼認為自己運行在目標 SoC上即可。超過必要的準確度只會讓模型在模擬器上的運行速度下降。實際上,任何層面的SoC建模,都要求我們把硬件和協議棧描述為比當前層面更低的一層,以便進行驗證。而且在理想的情況下,我們應該只要求夠用的準確度,以實現最高性能。

這種只為軟件層提供“夠用的準確度”的建模方法為不同的軟件開發人員提供了多種不同的建模環境,供他們在SoC項目的不同階段使用。可以采用SystemC這樣的語言進行事務處理層面的建模,創建出一個準確度低但速度足夠快的仿真器模型,用來同時運行許多應用。如果實時的真實數據的處理不是很重要,那么考慮采用虛擬原型方法比較好。

不過,必須完整運行整個軟件協議棧或處理真實環境中的數據時,最適合采用基于FPGA的原型方法。

使用原型驗證軟件的實例

只有采用基于FPGA的原型方法才能夠打破建模方法中準確度與性能之間內在的相互牽制關系。采用FPGA,我們既能實現實時的速度,又能以完全的RTL周期精度建模。這樣,單個原型不僅能供低層軟件驗證要求的準確模型使用,又能供高層應用開發人員需要的高速模型使用。實際上,整個SoC軟件協議棧都可以在單個基于FPGA的原型上建模。德克薩斯州奧斯汀市Freescale Semiconductor公司移動產品部的Scott Constable及其團隊開展的項目就是采用FPGA驗證軟件的一個很好的例子。

Freescale非常想加快SoC開發進程,因為手機市場上產品生命周期短,需要產品盡快打入市場。這不僅是為了贏得競爭,也是為了避免迅速過時。通過分析流程中耗時最多的環節,Freescale發現通過加快手機3G協議測試工作可以帶來最明顯的效果。如果測試工作能夠在流片前完成,Freescale就可以將項目時間縮短數月。與通常只有一到兩年的產品生命周期而言,這非常重要。

協議測試是一個復雜的過程,就算以較高的實時速度進行,也需要一天才能完成。采用FPGA是因為這是實現必要的時鐘速度,及時完成測試的唯一途徑。

評論