便攜式超高頻RFID讀寫器的FPGA實現(xiàn)

2 系統(tǒng)硬件電路設計

2.1 Cyclone EP1C3T144 FPGA最小系統(tǒng)

FPGA最小系統(tǒng)包含可編程門陣列、電源電路、時鐘電路、復位電路、配置電路、濾波電路。現(xiàn)場可編程門陣列采用EP1C3T144。它基于1.5 V,0.13μm全銅SRAM工藝、TQFP144封裝;104個I/O口,支持各種I/O標準;支持LVDS,數(shù)據(jù)傳輸率為311 Mbps;2910LE邏輯單元、

288 Kb RAM、1個PLL鎖相環(huán),支持66 MHz 32位PCI標準,支持外接133 MHz DDR SDROM;單獨有源時鐘接口,外接20 MHz頻率的有源晶振;專用配置電路接口,3.3 V LVTTL供電。FPGA基于SRAM技術,掉電數(shù)據(jù)易失,采用Altera公司配套的EPCS1JTAG下載模式。系統(tǒng)采用硬件和軟件復位:硬件復位接FPGA nconfig引腳,按下此鍵FPGA代碼從EEPROM重新配置;軟件復位是編寫代碼時設置reset引腳,按照代碼運行。

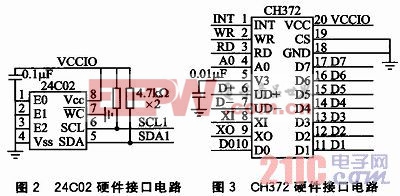

由于FPGA芯片內(nèi)部EEPROM空間有限,F(xiàn)PGA芯片外掛一個2KB EEPROM 24C02,24C02與400kHz I2C接口兼容。供電電壓為1.8~6.0V,供電電流為3mA,具有頁寫緩沖器和寫保護功能,SOP8封裝。它還具有讀寫次數(shù)多、保存時間長、功耗低的特點。24C02硬件接口電路如圖2所示。本文引用地址:http://www.104case.com/article/190983.htm

2.2 USB串行總線接口電路

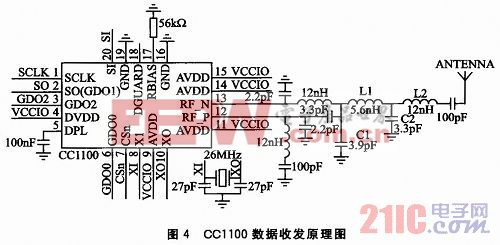

CH372簡易USB通用串行總線接口集成電路,兼容+5 V和+3.3 V供電,最大工作電流為30 mA,外接12 MHz頻率晶振,20引腳SOP封裝;兼容USB2.0數(shù)據(jù)傳輸協(xié)議,支持HID設備熱插熱拔,內(nèi)置USB底層通信協(xié)議,自動完成標準USB事件枚舉;支持數(shù)據(jù)控制傳輸、批量傳輸、終端傳輸;默認鏈接端點0所有事件,F(xiàn)PGA負責數(shù)據(jù)傳輸與處理,使用方便,CH372硬件接口電路如圖3所示。

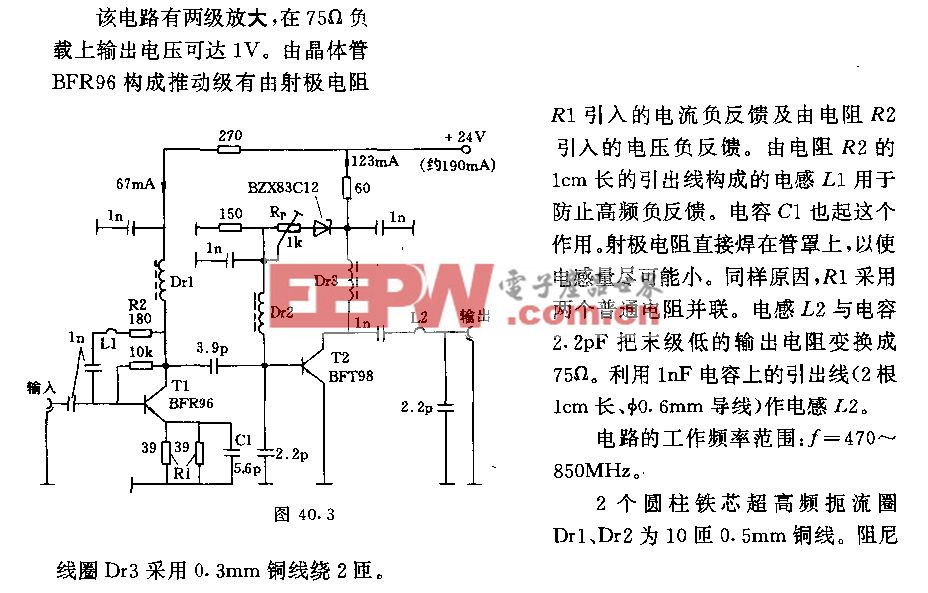

2.3 CC1100 RF收發(fā)電路

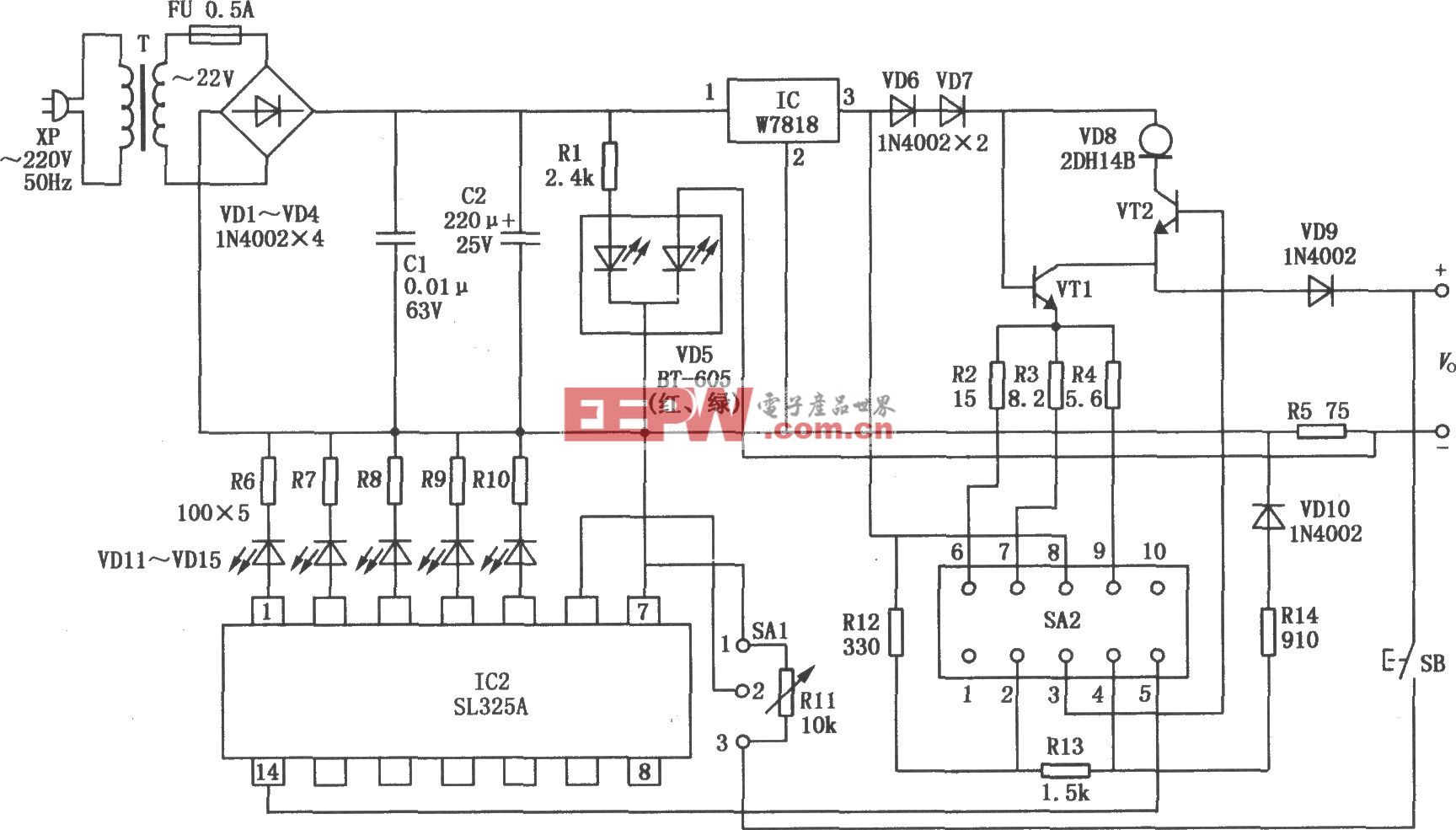

CC1100是一款極低功耗UHF收發(fā)集成電路。其通信效果好、抗干擾性能強、穿透力強、靈敏度高;可自由設置收發(fā)頻率,可設置范圍為300~348 MHz、400~464MHz、800~928 MHz,可編程控制數(shù)據(jù)傳輸速率最高可達500 kbps,4線SPI(SI、SO、SCLK、CSn)接口。CC1100正

常工作電壓為3.3 V,最高輸入電壓3.6 V,每個引腳輸入電壓應相同。868~915 MHz發(fā)送模式輸出功率為+10 dBm,電流為30 mA,接收最大功率為+10 dBm,硬件自動CRC校驗,支持ASK調(diào)制解調(diào),調(diào)整外圍元件可方便調(diào)整收發(fā)頻率。CC1100采用數(shù)據(jù)緩沖技術,具有2個64字節(jié)FIFO,緩沖發(fā)送和接收數(shù)據(jù)。CC1100可軟件設置RF發(fā)送功率、收發(fā)模式、調(diào)制格式、信道選擇和帶寬、數(shù)據(jù)傳輸速率、整機工作模式等。

CC1100屬于半雙工通信,接收和發(fā)送在射頻控制模塊RF CONTRON控制下分時進行,解調(diào)由積分器向下積分完成,AGC電路控制回路增益;調(diào)制基于直接頻率合成,載波信號由晶振與內(nèi)部PLL電路產(chǎn)生,發(fā)送模塊和接收模塊稍有區(qū)別。接收模塊包括:低噪聲放大器LAN、積分器INTEGRATION、模數(shù)轉(zhuǎn)換ADC、解調(diào)器DEMODU-LATOR、向前數(shù)據(jù)誤差處理器FEC/INTERLEAVER、包處理PACKET HANDLER、接收數(shù)據(jù)緩沖器RXFI FO、數(shù)字接口電路DIGITAL INTERFACE TO MCU;發(fā)送端與接收端不同的模塊有:壓控振蕩器VCO、混頻器MIXER、發(fā)送數(shù)據(jù)緩沖器TXFIFO,數(shù)據(jù)收發(fā)由不同模塊分時完成。

CC1100具有2種工作狀態(tài)——空閑狀態(tài)和工作狀態(tài),每種狀態(tài)對應電流不同。空閑狀態(tài)可分為等待WAIT狀態(tài),內(nèi)部電流1.9 mA;睡眠SLEEP狀態(tài),內(nèi)部電流400~900 nA;晶振的停振狀態(tài)僅維持寄存器值不變,內(nèi)部電流160 nA;工作狀態(tài)可分為接收(RX)和發(fā)送(TX)狀態(tài),接收狀態(tài)根據(jù)接收信號強弱內(nèi)部電流在14.2~15.4 mA范圍變化。發(fā)送狀態(tài)下,發(fā)送信號功率大小隨工作電流變化。14 mA時發(fā)射功率為-10 dBm,29 mA時發(fā)射功率為+20 dBm。根據(jù)工作狀態(tài)調(diào)整工作電流,可實現(xiàn)整機最低功耗。

由于采用ISO18000-6C標準射頻空中接口協(xié)議,系統(tǒng)采用889 MHz發(fā)射和接收頻率,改變CC1100第12、13引腳外接電容C1、C2,電感L1、L2的參數(shù)可調(diào)整射頻收發(fā)頻率,發(fā)射天線采用50 Ω偶極子天線。12、13引腳LC網(wǎng)絡器件參數(shù)可由軟件SmartRF studio仿真得到,參考CC1100官方DATASHEET,根據(jù)實際情況微調(diào)。CC1100數(shù)據(jù)收發(fā)原理圖如圖4所示。

評論