基于FPGA增量式編碼器的接口設計與實現

對以上3種計數方法進行分析可知,用純軟件計數雖然電路簡單,但是計數速度慢,微處理器工作量大,難以滿足實時性要求,想得到更高的指標,只能不斷地更換高性能微處理器,而且由于光電編碼器的轉速具有不可預見性,采用鎖相環進行倍頻的話會造成數據的不精確;而純硬件電路體積大且穩定性、可靠性差、調試煩瑣,而且當電阻、電容等組件參數變化時,會導致脈寬發生變化或不能產生具有穩定寬度

的脈沖。此外,RC電路抗干擾能力差,反饋部分易受外界干擾,在實際應用中會出現丟失脈沖現象,以至影響控制系統的精度和可靠性。

對于濾波、延時的處理方法很多,如微分型電路其信噪比小、抗干擾性差,積分型電路可以提高信噪比,但和微分型電路一樣有缺點:當輸入信號頻率高時,電容充放電不及時,導致輸出信號嚴重變形;對于各路倍頻電路來說,電阻和電容的參數不可能完全一致,所以倍頻后的各路脈沖寬度不等,而且寬度的調節也比較困難。設計采用的數字型延時電路可以很好地克服以上延時電路的缺點,延時的時間和各路倍頻的脈沖寬度由時鐘控制,倍頻后的脈沖寬度均勻一致。本文引用地址:http://www.104case.com/article/190932.htm

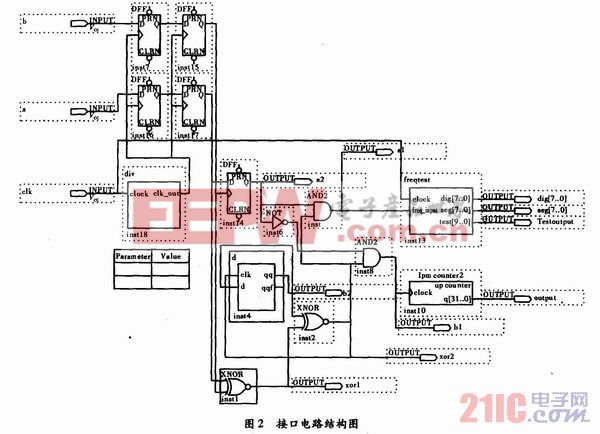

運用FPGA實現4倍頻、鑒相電路,采用全數字反饋電路的設計方法,由于倍頻、鑒相電路設計在同一芯片上,一方面,FPGA門電路高數量較大,時鐘頻率可達上百MHz的可編程邏輯器件,可以把他設計成所需的各種邏輯器件,可并行處理多項任務。因此處理速度比單片機或DSP快得多;另一方面,芯片內部的門電路、觸發器的參數特性完全一致,能保證在相同轉速下4倍頻脈沖信號的周期保持一致。作為板級芯片,電路做在芯片內部,其抗干擾能力比分離器件有很大提高。同時,由于現場可編程,可以方便地實現對電路的重新設計或修改,增強了系統的靈活性、通用性和可靠性。

3 仿真波形

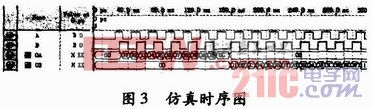

用Verilog HDL語言完成電路描述,各功能模塊運用原理圖方式進行描述,芯片采用Ahera公司Cyclone系列的EP1C12Q240C8N。在Quart-usII10.0環境下進行功能和時序仿真。編譯后結果如圖3所示,A、B即為差分整形電路的輸出,當A相超前B相時,輸出正向4倍頻脈沖,OA[7..0]為編碼器正轉時4倍頻脈沖個數;反之,輸出反向4倍頻脈沖,OB[7..0]為反轉時4倍頻脈沖個數。利用OA[7..0]與OB[7..0]可以方便地實現編碼器的可逆計數。

4 結束語

設計了增量式光電編碼器的一種簡單且高精度的鑒相、計數和接口電路,可根據光電編碼器的轉向進行遞增或遞減計數,并可與PC機、DSP、ARM等器件直接進行并行通訊。實驗結果驗證了設計的正確性。可以看出,利用FPGA設計光電編碼器信號處理模塊,無論是設計過程,還是電路結構、都變得更加簡潔。另外,在應用中注意FPGA的時鐘周期應小于編碼器脈沖的1/4,通常FPGA的時鐘已遠遠小于編碼器脈沖周期,故在FPGA中進行處理與計數是沒問題的。

文中FPGA實現的編碼器倍頻、鑒相電路,已經在激光跟蹤系統的項目中得到驗證,在系統中存在抖動及毛刺等干擾的情況下,仍能獲得穩定可靠的測量結果,并且可根據需要,任意改變參數以達到目的,這對正確和合理地使用編碼器,提高功能效益,從而在數控及機器人的死循環位置和速度控制系統中,提高位置調節精度、擴大速度調節范圍,都有良好的效果,是一種提高編碼器分辨率、實現角位移或轉速測量的優選電路。

評論