基于CPLD的線陣CCD驅動電路設計

2.5 電平轉換的電路設計

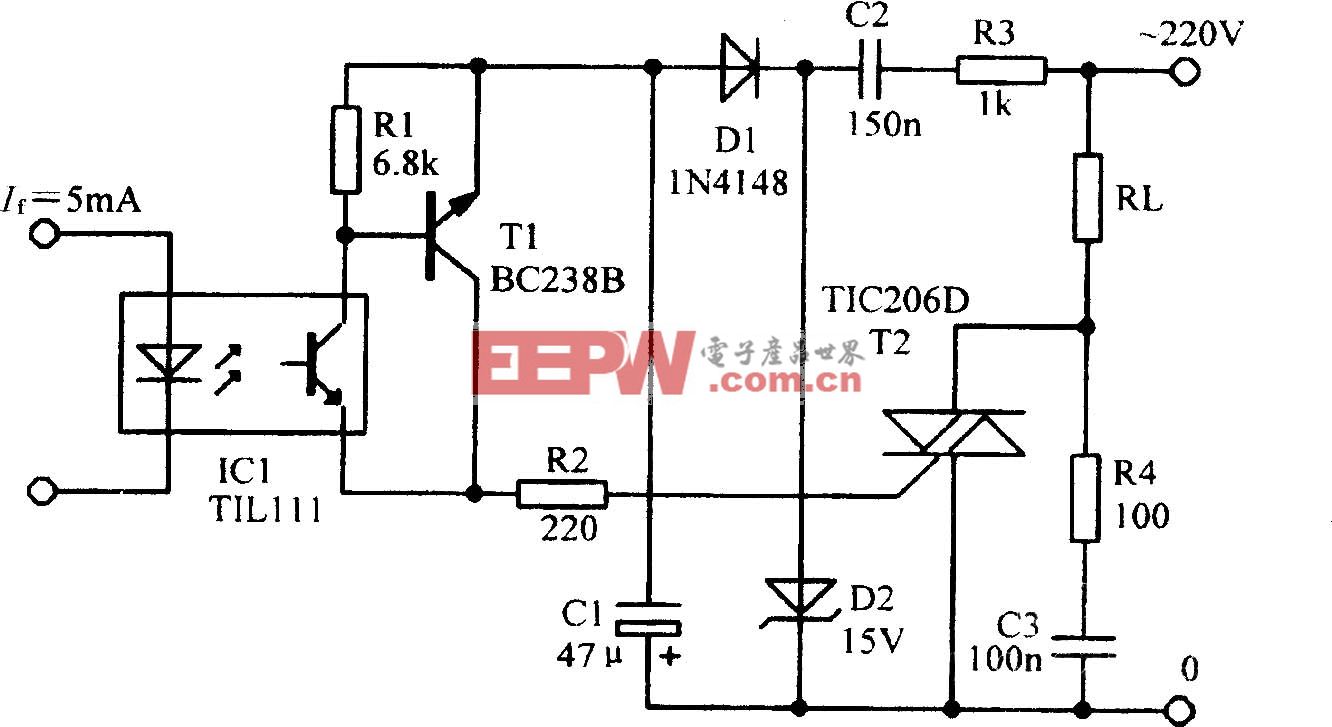

由于CPLD輸出的驅動脈沖電壓為3.3 V,而CCD工作所需的驅動脈沖為5 V,所以需要在CPLD和CCD之間加入—個電平轉換電路。電路原理如圖6所示。

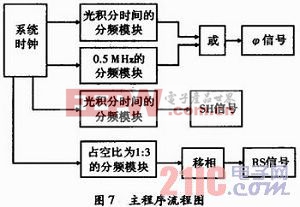

3 軟件設計

系統(tǒng)軟件采用Verilog HDL硬件描述語言,按照模塊化的思路設計,將要完成的任務分成為多個模塊,每個模塊由一個或多個子函數完成。這樣能使設計思路清晰、移植性強,在調試軟件時容易發(fā)現和改正錯誤,降低了軟件調試的難度。程序中盡量減少子函數之間的相互嵌套調用,這樣可以減少任務之間的等待時間,提高系統(tǒng)處理任務的能力。主程序如圖7所示。

SH是一個光積分信號,SH信號的相鄰兩個脈沖之間的時間間隔代表了積分時間的長短。光積分時間為5 416個RS周期,對系統(tǒng)時鐘進行光積分的分頻,實現了SH信號脈沖。在光積分階段,SH為低電平,它使存儲柵和模擬移位寄存器隔離,不會發(fā)生電荷轉移。時鐘脈沖φ為典型值0.5 MHz時,占空比為50%,占空比是指高電平在一個周期內所占的時間比率。它是SH信號和占空比為50%的一個0.5MHz的脈沖信號疊加,所以0.5 MHz的信號和SH信號通過一個或門,就可以實現φ信號;輸出復位脈沖RS為1 MHz,占空比1:3。此外,RS信號和SH、φ信號有一定的相位關系,通過一個移位寄存器移相,來實現RS脈沖信號。

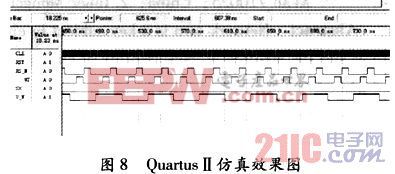

4 仿真實驗

系統(tǒng)時鐘周期部分設置為1 ns,正常工作時復位信號RS為高電平,然后對RS、φ、SH信號進行仿真,結果如圖8所示。

5 結束語

研究的線陣CCD驅動電路主要是以CPLD為驅動中心而設計,這種方案減少了以往驅動電路的電路體積大、設計復雜、調試困難等缺點,增加了系統(tǒng)的穩(wěn)定性、可靠性,集成度高且抗干擾能力強。通過對硬件和軟件大量的模擬實驗表明,文中所研究的線陣CCD驅動脈沖信號能夠滿足CCD工作所需的基本功能,達到了設計要求。

評論