基于CPLD的簡易數字頻率計的設計

2.2.3 鎖存電路模塊

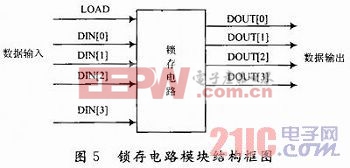

鎖存電路模塊可使顯示電路的工作穩定而可靠,避免計數電路模塊清零時引起顯示閃爍的現象。鎖存電路模塊是由多個鎖存器組成。每個鎖存器都是用來鎖存與其單獨相連的計數器的輸出數據。由于每個鎖存器鎖存的都是4位二進制代碼表示的十進制數,其功能完全相同,因此只需要設計制作一個鎖存器就可連接組合成一個鎖存電路模塊。為實現其功能,鎖存器需設置一個使鎖存器工作的使能端LOAD,四個數據輸入端即DIN[0],DIN[1],DIN[2]和DIN[3],并由它們輸入計數器的計數值,還需設置四個鎖存數據的輸出端:即DOUT[0],DOUT[1],DOUT[2]和DOUT[3]。鎖存電路模塊中單個鎖存器的符號及端口功能如圖5所示。本文引用地址:http://www.104case.com/article/190886.htm

2.2.4 譯碼電路模塊

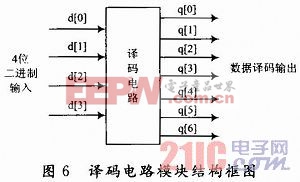

譯碼電路模塊可對表示十進制數的4位二進制代碼進行編碼,此模塊可直接連接數碼管驅動器,從而驅動數碼管顯示出相應的阿拉伯數字等字符。與鎖存器電路模塊設計一樣,它也只需要先設計一個單個的譯碼器,然后通過連接組合就可構成譯碼電路模塊,從而實現譯碼功能。為實現其功能,單個譯碼器需要設置4個數據輸入端:即d[0],d[1],d[2]和d[3],并由這些端口輸入鎖存電路模塊輸出的4位二進制數據,需要設置7個輸出端:即q[0],q[1],q[2],q[3],q[4],q[5]和q[6],它們分別連接7段數碼管的7個顯示輸入端。譯碼電路模塊中單個譯碼器符號及端口功能如圖6所示。

3 軟件設計

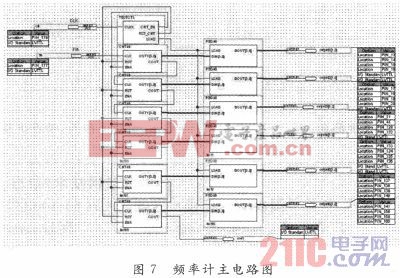

根據前面的分析,采用VHDL語言設計一個簡易的數字頻率計,運用自頂向下的設計思想,將系統按功能逐層分割的層次化設計方法進行設計。在頂層對內部各功能塊的連接關系和對外的接口關系進行了描述,而功能塊的邏輯功能和具體實現形式則由下一層模塊來描述。即控制、計數、鎖存、譯碼四個實現數字頻率計的核心模塊,然后根據圖2可以將上述四個模塊VHDL源程序作為底層元件,使用QuartusⅡ開發工具,用該工具軟件所支持的語言——硬件描述語言VHDL,以文本的方式進行編程輸入。在編程時分別對控制、計數、鎖存、譯碼等電路模塊進行VHDL文本描述,使每個電路模塊以及器件都以文本的形式出現,然后通過編譯、波形分析、仿真、調試來完善每個器件的功能。單個器件制作完成后,然后將它們生成庫文件,并產生相應的符號,最后用語言將各個己生成庫文件的器件的各個端口連接在一起,從而形成了頻率計主電路的軟件結構。在連接器件時,采用圖形輸入方式,即在圖形輸入界面中調出先制作好的庫文件器件符號,再將每個器件符號的各端口直接連線,從而構成頻率計主電路圖。頻率計主電路圖如圖7所示。仿真波形如圖8所示。

評論