反輻射導彈抗誘騙性測試系統UI設計

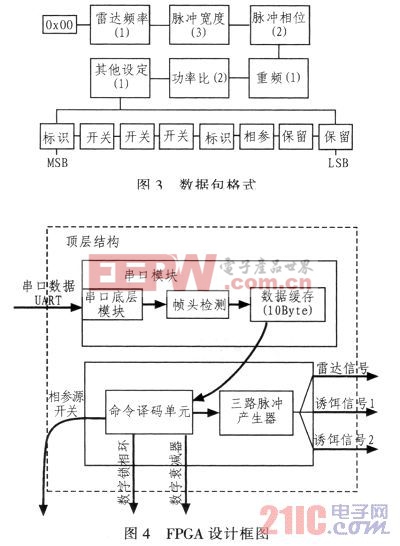

用戶將參數輸完后,點擊設置鍵,此時mini2440通過串口將信息發送給FPGA。為同步數據,將每個數據包的開頭加入起始位,用來進行同步。數據包如圖3所示。本文引用地址:http://www.104case.com/article/190795.htm

3 FPGA模塊設計

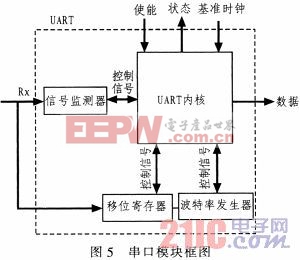

此部分是整個系統的中樞,用于將用戶命令轉換為控制信號來控制各個器件的工作狀態,其中被控器件包括數字鎖相環,數字衰減器,FPGA同時產生視頻信號。

FPGA內部主要包舍有3個模塊,內部結構框圖如圖4所示。

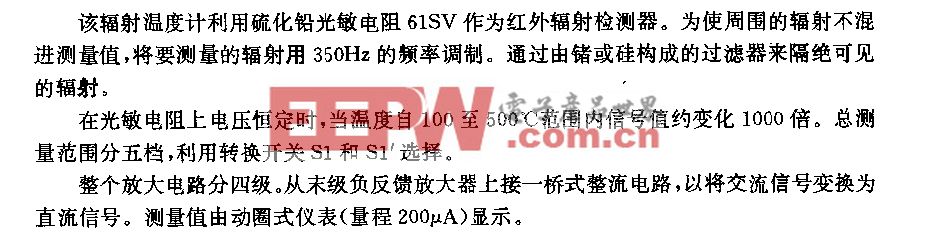

在串口模塊中,主要分為3大部分,串口底層模塊,包頭檢測,數據存儲。其中串口底層模塊設計框圖圖5所示。

外圍器件SP3223將BS232電平轉換為CMOS電平并通過Rx傳給FPGA。當使能有效時,UART模塊首先檢測起始位,如果有效,則屏蔽信號監測器,由UART內核按波特率時鐘對八位數據位進行同步接收,并判斷最后一位終止位是否為‘1’,如果滿足要求,則將此幀數據放到數據總線上,并給狀態信號上置10個時鐘周期的高電平。讀完九個數據后,重新使能信號監測器等待下幀數據。本系統中波特率設為19 200,全局時鐘為50 MHz,分頻器分頻系數用以下公式計算divide=freq/baudrate≈2 604。

當串口模塊處理完一包數據之后,將數據包以數組的形式傳給操作模塊,并使能操作模塊。操作模塊進行數據包解碼,將數據包拆包,將數據分別傳給視頻信號產生器和相應I/O端口。

由于三路視頻信號之間存在相位關系,因此以第一路雷達信號為基準,設定一個較大的統一延時量,在此基礎上進行加減,即為各路視頻信號的相位信息。這種方法簡單高效。

評論