USB3.0中五分頻電路設計

3 仿真結果與分析

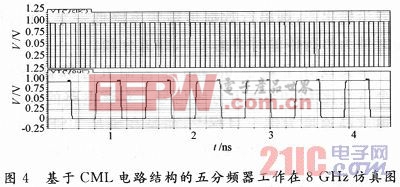

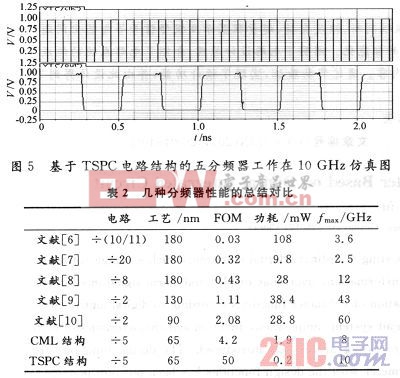

采用Cadence公司的spectre仿真器對設計的分頻器分別仿真,仿真電源電壓為1 V,結果表明:在典型工藝參數條件下,基于CML電路結構的五分頻器最大工作頻率是8 GHz,最小工作頻率是1 kHz,當工作在8 GHz時,功耗為1.7 mW,輸出信號占空比為49.76%;基于TSPC電路結構的五分頻器最大工作頻率是10 GHz,最小工作頻率是10 MHz,當工作在10GHz時,功耗采用10 ns內的平均功耗,功耗為0.2mW,輸出信號占空比為49.92%。由于是單端輸入輸出,基于TSPC電路結構的分頻器抗噪聲能力較弱。最高工作頻率下的仿真結果如圖4,圖5所示。本文引用地址:http://www.104case.com/article/190786.htm

對于不同頻率的分頻器。通常采用FOM值來比較其性能,分頻器的FOM值定義為:

FOM=fmax/P

式中:fmax是分頻器的最高工作頻率;P是分頻器在最高工作頻率下的功耗,表2為本文設計的分頻器和其他文獻中介紹的分頻器作對比,所有的分頻器均采用CMOS工藝,對比表明本文設計的5分頻器性能較優,在65 nm工藝下具有明顯的功耗低優勢,尤其是采用TSPC電路結構的分頻器,功耗極低。

4 結語

本文基于65 nm工藝分別采用CML電路結構和TSPC電路結構設計了1個五分頻器,采用spectre仿真表明,采用CML結構的分頻器最高工作頻率8 GHz,功耗1.7 mW,輸出信號占空比49.76%;采用TSPC電路結構分頻器最高工作頻率10 GHz,功耗為0.2 mW,輸出信號占空比49.91%,由于采用單端輸入輸出,所以采用TSPC結構的分頻器抗噪聲能力較弱。輸出信號占空比為50%是本文一大特點,2種結構的分頻器工作頻率完全覆蓋了USB 3.0協議所要求的頻率范圍,滿足協議要求。

評論