USB3.0中五分頻電路設計

2 分頻器基本電路的設計

觸發器是整個分頻器中最基本的結構,只有設計好一個快速的觸發器,才能實現一個高頻率的分頻器,目前用于分頻電路的觸發器電路主要有3種。第1種是CML(Current Mode logic)電路,是由ECL(EmitterCouple Logic)電路演變來的,相比傳統的靜態分頻器,由于電路的擺幅較小,因而電路的工作速度快;第2種是TSPC(True Single Phase Clock)電路,采用單相時鐘,大大減少了電路的元件數目,從而提高電路工作速度,同時這種電路功耗極低;第3種是注鎖式(Injected Locked)電路,由于要使用電感,因而它的體積過大且工藝難度高,成本較高,很少被廣泛采用。本文分別采用CML電路和TSPC電路構成分頻電路,并對兩者的速度和功耗等進行比較。

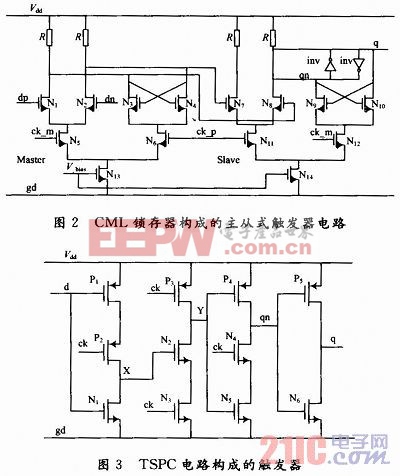

CML電路構成的觸發器如圖2所示,由圖中可以看出,該觸發器由2個CML結構鎖存器組成,它們構成主從型結構,每個鎖存器都要經過2個階段:跟蹤階段和保持階段。當主鎖存器跟蹤輸入信號時,從鎖存器處于鎖存保持階段,然后交替。其中N13,N14為尾電流管,偏置電壓V_ biss使N13,N14管工作在飽和狀態,充當恒流源的作用。dp和dn是由輸入信號d經傳輸門和反相器產生的一對互補差分信號,cK_m和ck_p是由輸入時鐘信號clk經傳輸門和反相器產生的一對互補時鐘差分信號。主鎖存器工作狀態為:當cK_m為高電平時,N5管導通,N6管關閉,此時N1,N2管工作在差分狀態,將輸入信號dp,dn采入。當cK_p為高電平時,N6管導通,N5管關閉,此時N3,N4使電路維持在鎖存狀態,從鎖存器工作狀態恰好與主鎖存器工作狀態相反。設計中在觸發器輸出端q,qn之間加了2個反相器從而在q,qn之間形成正反饋,增強了電路的輸出驅動能力。工作時,電路的尾電流應當足夠大,有利于提高電路工作頻率和輸出信號的擺幅。本文引用地址:http://www.104case.com/article/190786.htm

TSPC電路構成的觸發器如圖3所示,由圖中可以看出,該電路由四級反相器構成,上升沿觸發,當CK為低電平,輸入反相器在節點X上采樣反向d輸入,第2級反相器處于保持狀態,節點Y預充電至Vdd,第三級反相器處于保持狀態,時鐘上升沿來時,第二級反相器求值,Y的電平值發生變化,時鐘ck為高電平時,節點Y的值傳送到輸出q,該觸發器的延時為4個反相器的傳播延時,由于電路中元件數目很少,而且采用動態邏輯,因此功耗極低。

評論