基于FPGA的真彩VGA顯示的實現(xiàn)

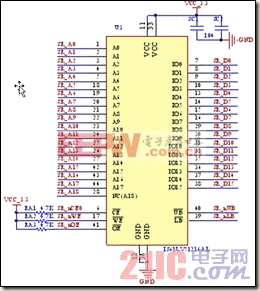

(3)SRAM:VGA刷屏數(shù)據(jù)顯存IC,此處采用了ISSI的IS61LV51216AL-10TI 作為高速顯存芯片。

2. 軟件設(shè)計

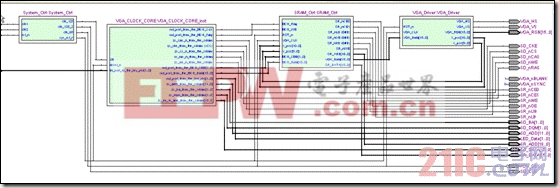

如上圖所示,Bingo設(shè)計的真彩圖像顯示的工程的RTL圖。

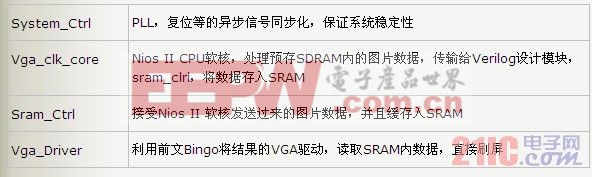

這應(yīng)該算是真彩顯示的最簡單的設(shè)計吧,將圖像數(shù)據(jù)隨Nios II配置JTAG下載SDRAM,再讀取專一值SRAM,刷屏實現(xiàn)真彩圖像的VGA顯示。本工程的軟件架構(gòu)如下,主要用了以下這幾個模塊:

3. 注意問題

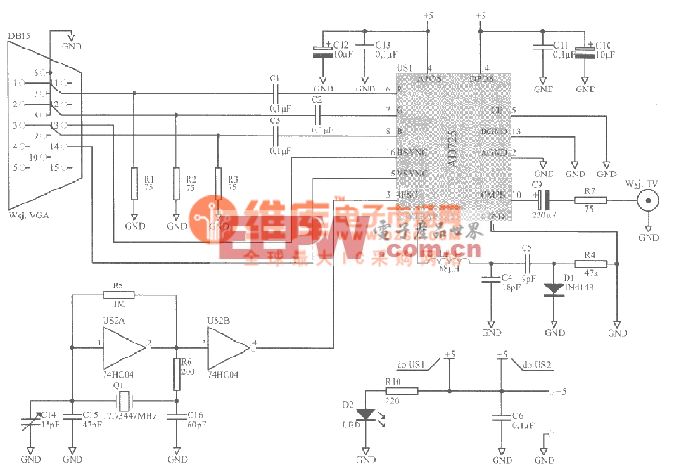

關(guān)于CPU傳輸數(shù)據(jù)給Sram_Ctrl模塊,Bingo采用了模擬6800總線協(xié)議,來對數(shù)據(jù)進行交換處理。當然若有更好的方案,您可以自行設(shè)計協(xié)議,Verilog相當?shù)撵`活。

關(guān)于時鐘的處理,由于設(shè)計中設(shè)計到了大量數(shù)據(jù)的傳輸,時序上需要嚴謹,因此要嚴格處理好CPU與Verilog的跨時鐘、VGA刷屏時鐘、復位信號等的協(xié)調(diào),以及穩(wěn)態(tài)亞穩(wěn)態(tài),甚至時序約束。

評論