一種基于FPGA的無線射頻讀卡器開發(fā)與設(shè)計(jì)

Xilinx千兆以太網(wǎng)系統(tǒng)參考設(shè)計(jì)(GSRD)是一個(gè)基于 EDK 的參考系統(tǒng),能夠在基于TCP/IP的協(xié)議接口和用戶數(shù)據(jù)接口之間搭起一座高性能的橋梁。GSRD的組件具備滿足TCP/IP系統(tǒng)每比特和每包開銷要求的功能。

Xilinx還針對Monta Vista Linux和 Treck堆棧提供了發(fā)射性能基準(zhǔn)。采用 Xilinx Platform Studio (XPS)微處理器庫定義的Nucleus PLUS RTOS,為采用MicroBlaze和PowerPC處理器的系統(tǒng)帶來了新的優(yōu)勢。Nucleus PLUS RTOS尺寸很小,這意味著它能夠利用片上現(xiàn)有的存儲器,從而最大限度降低功耗,提高性能。此外,廣泛的中間件使得Nucleus PLUS RTOS成為RFID后端網(wǎng)絡(luò)的理想選擇。

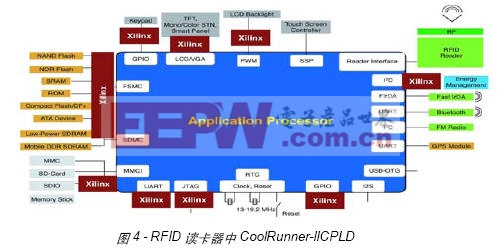

利用XilinxCoolRunnerTM-II型CPLD,手持式射頻讀卡器可連接至硬盤驅(qū)動(dòng)器、QWERTY鍵盤、可移動(dòng)硬盤接口、各種顯示設(shè)備和其他計(jì)算機(jī)外設(shè)(如圖4所示)。這些CPLD還能幫助應(yīng)用處理器,并且滿足低功耗、高性能和更小芯片封裝等要求。

結(jié)論

將來,射頻讀卡器很可能具備前端 DSP功能,譬如射頻協(xié)議處理等。如今,這些功能在獨(dú)立式DSP中進(jìn)行處理,將來,它們很有可能被集成于FPGA。嵌入式軟處理內(nèi)核已可顯著提升DMIPS/MHz性能,不久以后,高版本的處理內(nèi)核將取代控制讀卡器應(yīng)用程序的后端外部處理器,從而借助可編程邏輯最大限度地提高射頻讀卡器設(shè)備的靈活性,同時(shí)最大限度降低其成本。

評論