一種交織器和解交織器的FPGA電路實現

電路特點分析

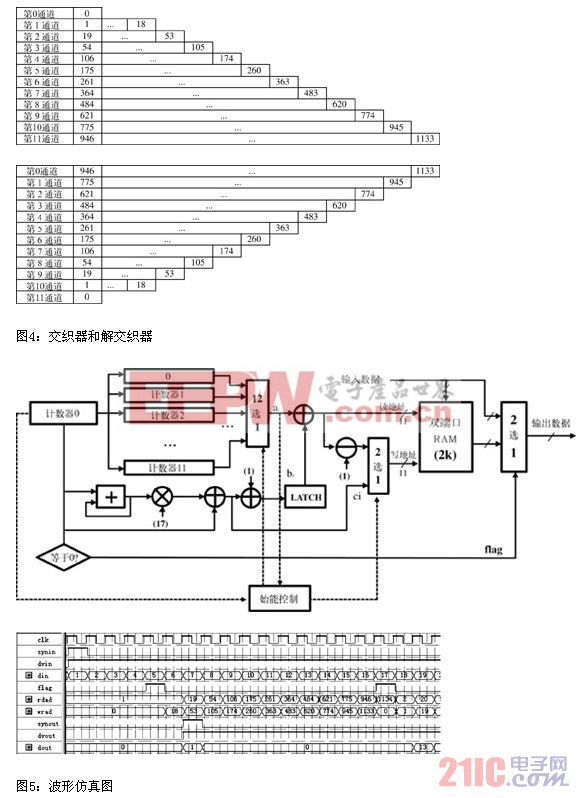

本設計采用單倍實現所用的存儲單元總數Nram=[(I-1)×M/2+1]×I=1134,相應要用到地址總線的位數為Nad=ceil[log2(Nram)]=11。也就是說,要用到2k的雙端口RAM,讀寫地址線各11根。

而采用一般的雙倍實現占用的存儲單元總數Nram=[(I-1)×M+1]×I=2256,相應要用到地址總線位數Nad=ceil[log2(Nram)]=12。如果采用雙倍實現,要用到4k的雙端口RAM,讀寫地址線各12根。

理論上最簡存儲單元的占用量為Nram=[(I-1)×M×I/2 =1122,地址總線位數為Nad=ceil[log2(Nram)]=11,所以單倍實現的優點是顯而易見的,其占用存儲單元數為雙倍實現的一半,讀寫地址線各少1根,接近于最簡占用量。只要交織深度I不是很深,該設計方法使用的邏輯單元門數并不多,而且可以節約大量的存儲單元,效果是顯而易見的。

評論