基于單片機及FPGA的程控濾波器設計與實現

濾波器是一種用來消除干擾雜訊的器件,可用于對特定頻率的頻點或該頻點以外的頻率進行有效濾除。它在電子領域中占有很重要的地位,在信號處理、抗干擾處理、電力系統、抗混疊處理中都得到了廣泛的應用。而對于程控濾波器,該系統的最大特點在于其濾波模式可以程控選擇,且-3dB截止頻率程控可調,相當于一個集多功能于一體的濾波器,將有更好的應用前景。此外,系統具有幅頻特性測試的功能,并通過示波器顯示頻譜特性,可直觀地反應濾波效果。

本文引用地址:http://www.104case.com/article/190584.htm1方案論證與選擇

1.1可變增益放大模塊的設計與論證

方案1:數字電位器控制兩級INA129級聯。用FPGA控制數字電位器DS1267使其輸出不同的阻值,作為高精度儀表放大器INA129的反饋電阻。通過控制數字電位器來改變INA129的放大倍數,從而實現放大器的增益可調。

方案2:采用可變增益放大器AD603實現。可變增益放大器內部由R-2R梯形電阻網絡和固定增益放大器構成,加在其梯型網絡輸入端的信號經衰減后,由固定增益放大器輸出,衰減量是由加在增益控制接口的參考電壓決定;可通過單片機控制,由DAC產生精確的參考電壓控制增益,從而實現較精確的數控。

由于輸入的正弦小信號振幅10mV,電壓增益60dB,10dB步進程控可調,且電壓增益誤差不能大于5%。對精度而言兩個方案都可實現,在AD603后再加一級放大也可實現60dB的放大倍數。但數字電位器內部結構復雜,有電容影響,后級接運放后會帶來意想不到的后果,因此采用方案2。

1.2濾波器模塊的設計與論證

方案1:采用數字濾波器。利用MATLAB的數字濾波器設計FIR或者IIR濾波器。數字濾波器具有精度高,截止特性好等優點。但是FIR濾波器會占用太多FPGA資源,IIR濾波器設計時工作量大且穩定性不高,且要使截止頻率可調,必須使用不同的參數,設計起來軟件量比較大。

方案2;采用無源LC濾波器。利用電感和電容可以搭建各種類型的濾波器。參照濾波器設計手冊上的相關參數,可以比較容易地設計出理想的濾波器。但是如果要截止頻率可調,只有改變電感電容參數,硬件會非常復雜。

方案3:采用集成的開關電容濾波器芯片。開關電容濾波器是由MOS開關、MOS電容和MOS運算放大器構成的一種大規模集成電路濾波器。其開關電容組在時鐘頻率的驅動下,可以等效成一個和時鐘頻率有關的等效電阻。當用外部時鐘改變時,等效電阻改變,從而改變了濾波器的時間常敦,也就改變了濾波特性。開關電容濾波器可以直接處理模擬信號,而不必像數字濾波器那樣需要A/D、D/A變換,簡化了電路設計,提高了系統的可靠性。

綜上所述,本系統采用方案3,利用集成芯片MAX297實現低通濾波器,利用LTC1068實現高通濾波器;采用方案2,利用無源LC濾波器技術來實現四階橢圓低通濾波器。

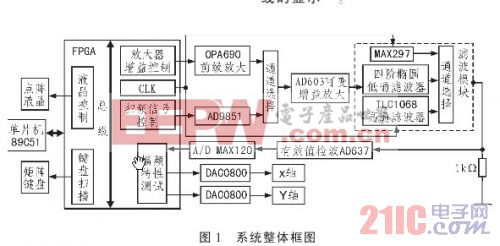

2系統總體設計方案及實現方框圖

本系統以單片機及FPGA為控制核心,由可控增益放大模塊、程控濾波模塊和幅頻特性測試模塊構成。系統框圖如圖1所示。輸入振幅為1V的信號經分壓網絡衰減后變成振幅10mV的小信號,經OPA690前級放大2倍,同時起到阻抗變換和隔離的作用。與此同時由AD9851產生一設定頻率的正弦信號,通過模擬開關選擇一道送到后級。信號由程序控制AD603進行0~60dB的可調增益放大后,送入濾波模塊。濾波模塊包括低通、高通、橢圓濾波器,其中低通、高通由程序控制-3dB截止頻率在1~30kHz范圍內可調,步進1kHz。橢圓濾波器截止頻率50kHz。再通過模擬開關選擇某一特定濾波信號輸出,經有效值檢波和A/D轉換后送入FPGA進行幅頻特性的測試,再用兩塊DAC0800實現幅頻特性曲線的顯示。

3主要功能電路設計

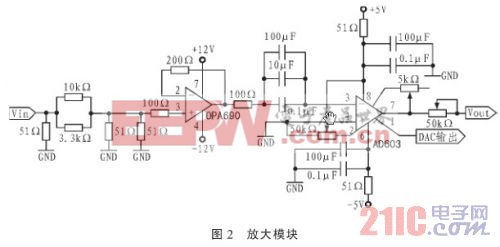

3.1放大模塊

放大模塊的具體電路如圖2所示。第一部分是一個分壓網絡,其中前4個電阻將輸入信號衰減100倍,并與信號源內阻共同構成51Ω阻抗,后面的51Ω為匹配電阻。第二部分采用OPA690將小信號放大2倍,同時起到阻抗變換和隔離的作用。由于AD603輸入阻抗為100Ω,所以在后面串接一個100Ω的電阻進行匹配。第三部分即為AD603可變增益放大,它的增益隨著控制電壓的增大以dB為單位線性增長。1腳的參考電壓通過單片機進行運算并控制DAC芯片輸出電壓來得到,從而實現精確的數控。增益G(dB)=40VG+G0,其中VG為差分輸入電壓,范圍-500~500mV;G0是增益起點,接不同反饋網絡時也不同。在5、7腳間接一個5kΩ的電位器,從而改變。

評論