基于FPGA的混合擴頻發射機設計與實現

摘要:以Alter公司的FPGA為硬件平臺,以QuartusⅡ為設計工具,來實現該直擴/跳頻混合發射系統。頂層采用圖形設計方式,各個模塊均采用Verilog語言進行設計。編碼模塊采用了RS(255,223)碼與卷積碼(2,1,7)相結合,擴頻模塊采用GOLD碼序列進行擴頻,調制模塊采用MSK調制。仿真結果表明:各個仿真模塊均滿足設計的要求,整個系統輸出穩定無毛刺,達到了預期的效果。

關鍵詞:直擴/跳頻;發射機;Verilog HDL;MSK

0 引言

擴頻通信是將待傳輸的信息數據用偽隨機序列進行調制,實現頻譜擴展后再發射出去進行傳輸。在接收端,使用與發射端相同的偽隨機碼對接收到的信號進行相關處理,恢復出原來的信息。直擴/跳頻(DS/FH)混合模式是一種有效的方法,它結合了直擴擴頻與跳頻擴頻的優點,消除了直擴擴頻與跳頻擴頻的局限性,可廣泛應用于軍事通信中,達到更好的抗干擾效果。

該設計以FPGA為硬件平臺,以QuartusⅡ為設計工具來實現直擴/跳頻(DS/FH)發射機的。頂層采用圖形設計方式,各個模塊均采用Veri log語言進行設計,編碼模塊采用了RS(255,223)碼與卷積碼(2,1,7)相結合,擴頻模塊采用GOLD碼序列進行擴頻,調制模塊采用MSK調制。

1 發射系統的總體框圖

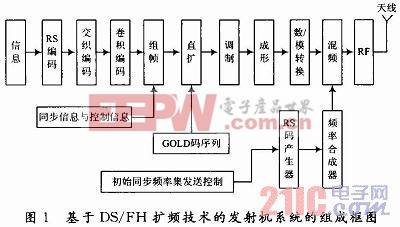

所設計的發射機系統主要包括:信道編碼器、組幀電路、直擴部分、成形電路、調制器、數/模轉換器、頻率合成器、RS碼產生器、混頻器、功放、天線等。組成框圖如圖1所示。

射頻部分主要采用跳頻技術將中頻信號進行頻譜搬移,通過跳頻調制和高頻混頻兩步完成,用到頻率合成技術和濾波等,這主要通過硬件實現。基帶部分則完成FPGA的設計,下面將詳細介紹。

主要可以劃分為以下幾個模塊:編碼模塊、組幀模塊、擴頻模塊、調制模塊。編碼模塊完成信息的RS編碼和卷積編碼;組幀模塊在經過編碼的數據前面添加位同步和幀同步信息;直接序列擴頻模塊將信號頻譜擴展到一個很寬的頻段上;MSK調制模塊利用擴頻序列去調制載波,將擴頻調制信號搬移到射頻上去,然后經過功率放大,D/A變換發送出去。

2 各個發射模塊的功能介紹及設計

2.1 編碼模塊設計

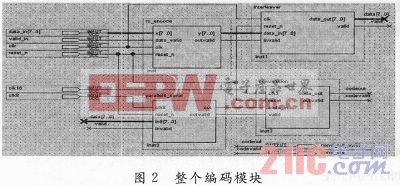

整個編碼實現由4級組成,分別是RS編碼、交織、并/串轉換和卷積編碼,如圖2所示。

評論