一種通用的FPGA位元電路

摘要:針對目前不同類型FPGA要求的位元電路不一致現象,提出了一種通用的FPGA位元電路,該位元電路不僅適用于任意結構的反熔絲/熔絲FPGA,還可以單獨的存儲1和0,對反熔絲/熔絲熔通后的電阻特性也沒有具體要求。

關鍵詞:現場可編程邏輯門陣列;反熔絲;位元電路;邏輯模塊

FPGA (Field Programmable Gate Array), 即現場可編程邏輯門陣列,是當今集成電路半定制設計中的重要組成部分,具有結構靈活,功能完善,集成度高,設計周期短的特點,受到了越來越多的用戶的歡迎;并且隨著集成電路工藝制程的不斷更新,FPGA的速度也得到了極大的提高。FPGA一般分為反熔絲型、EPROM型及SRAM型。

基于Flash的FPGA一般需要采用特殊的結構,造價很高;基于SRAM的FPGA器件雖然不需要特殊的工藝,可以用一般的CMOS工藝實現,但是這種FPGA的保密性及可靠性都不高;反熔絲/熔絲FPGA的保密性及可靠性都很高,市場上也有很多的反熔絲/熔絲結構,有些完全可以于CM OS工藝兼容。因此反熔絲/熔絲FPGA具有很好的發展前景。

在反熔絲/熔絲FPGA中,反熔絲/熔絲結構對FPGA的性能至關重要,這些反熔絲/熔絲結構擊穿后的電阻特性不一致,大至10K歐姆,小的只有幾歐姆,因此基于反熔絲/熔絲結構的位元電路需要單獨設計。在本論文中提出的這種位元電路對反熔絲/熔絲結構擊穿后的電阻沒有特殊要求,因此具有重復利用性。因為篇幅有限,在此只敘述此位元電路在反熔絲FPCA中的應用,此位元電路可以完全應用到熔絲FPCA中。

1 新型反熔絲/熔絲位元電路

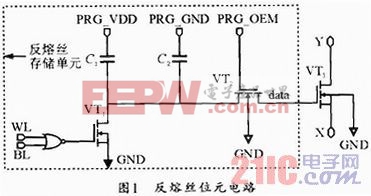

反熔絲/熔絲位元電路是控制反熔絲/熔絲完成邏輯編程的電路,圖1所示是反熔絲位元電路,實框中是反熔絲存儲單元電路圖,該存儲單元可以單獨的存儲0和1。寫狀態時加編程高壓,讓其中一個反熔絲電容熔通為一個小電阻,另一個反熔絲電容保持原狀態;讀取時,在熔通電容一端加電源電壓,通過熔通后的小電阻傳輸高電平,完成1的存儲;在熔通電容一端加低電平,通過熔通后的小電阻傳輸低電平,完成0的存儲。可見位元電路輸出高低電平是根據節點電壓的變化來判斷,與節點電流沒有關系,因此對擊穿后的電阻特性沒有特殊要求。

對于熔絲位元電路只需將反熔絲結構換成熔絲結構,寫狀態時加編程高壓,讓其中一個熔絲熔斷,另一個熔絲保持常態;讀取時,在保持常態的熔絲一端加電源電壓,通過熔絲傳輸高電平,完成1的存儲,在保持常態的熔絲一端加低電平,通過熔絲傳輸低電平,完成0的存儲。

圖1的框外是一個MOS管,此MOS管是作為開關用的,當data輸出0時,此開關關閉,X0與Y0斷開,當data輸出1時,此開關打開,X0與Y0實際上是連在一起的,此時從X0輸入信號,Y0的輸出信號即為X0。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論