一種基于FPGA的紅外視頻采集系統設計

圖3為SignaltapII觀測到的圖像數據采集時序。hactive_even高電平期間為有效圖像數據采集階段,yuvdin為從ADV7181B輸出的8位并行圖像數據.當“FF 0000 ε0”到來時,開始采集偶數場圖像的一行有效像素,其中黑線分隔的reg1、reg2、reg3為提取的3路即將送入RGB轉化模塊的圖像數據。

2.3 YUV2RGB轉化模塊

VGA顯示器所需的圖像數據為RGB格式,所以需要對YCrCb進行轉化,轉化公式如下:

R=1.1 64(Y-16)+1.596(Cr-128) (1)

G=1.164(Y-16)-0.81 3(Cr-128)-0.392(Cb-128) (2)

B=1.1 64(Y-16)+2.017(Cb-128) (3)

浮點運算需要大量的FPGA資源,進而影響系統性能,本系統采用查找表來簡少FPGA運算量,將上式中5個不同的系數分量分別編寫查找表。為進一步簡化運算將(1)式兩邊乘以2,以式(1)為例,查找表如下:

設a=2×1.1 64Y.b=2×1.596Cr式(1)簡化為:2R=a+b-446。若(a+b)>446,則R分量值為(a+b446)/2;若(a+b)446,則R分量值為0。

同理可算出G、B分量,即完成了YCrCb到RGB的轉化。由于SRAM數據線為16位,各取3路8位RGB分量的R信號(5位),G信號(6位),B信號(5位)寫入SRAM。當RGB_wrdata為非零圖像數據時,將其寫入SRAM即實現了分辨率由720×525向360×250的轉化。

2.4 SRAM讀寫控制模塊

當寫入360×250的視頻流數據量所需的存儲空間為100KB時,由于FPGA內部存儲資源有限,本系統通過外部SRAM來存儲圖像數據。SRAM所使用的型號為IS61LV25616,存儲空間為256K×16位,滿足圖像存儲需求。SRAM芯片工作不需要刷新,讀寫時序也不復雜,當向SRAM寫入數據時先建立地址和數據,然后使能寫信號wr_n,在wr_n保持一定時間后將其復位,最后釋放地址總線和數據總線;當從SRAM中讀出數據時,置wr_n為高電平,同時使能SRAM讀出信號,并建立地址。一幀圖像的偶場信號寫入SRAM的波形如圖4所示。本文引用地址:http://www.104case.com/article/190429.htm

2.5 VGA控制模塊

ADV7123是一個3路10位信號輸入的高速D/A芯片,采樣速度最高可達330MHz,可用于多種顯示系統。本文采用標準的VGA顯示模式640 ×480@60 Hz,VGA水平/垂直時序參數如表4、表5所列。

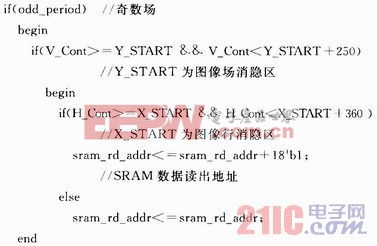

VGA控制模塊產生ADV7123的工作時序,當一幀圖像的偶數場寫入SRAM時,奇數場時間段則不再向SRAM中寫數據,而是從SRAM中讀出圖像數據,這樣即可實時傳輸圖像。為了實現圖像的完整性,640×480可顯示區域為360×250,具體代碼如下:

評論