基于CPLD技術(shù)的看門狗電路設(shè)計(jì)

看門狗電路的設(shè)計(jì)

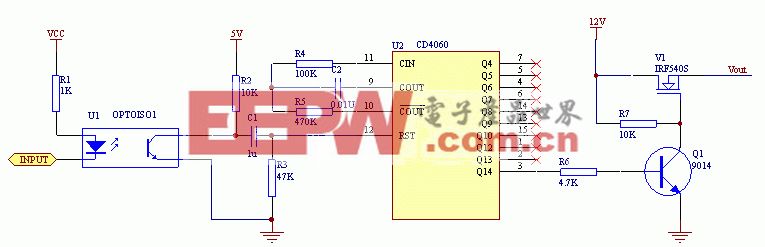

其中,CLKIN為32762Hz方波信號(hào),CLR為分頻器清零端,TIMECLK為32分頻器的輸出端。由該圖可見,當(dāng)CLR為低電平時(shí),分頻器工作,CLR為高電平時(shí),分頻器清零。

3.2 計(jì)數(shù)定時(shí)電路

該電路是看門狗的核心電路,其功能由圖1中的U5 COMP宏單元來完成,該宏單元由一個(gè)8位的二進(jìn)制計(jì)數(shù)器、一個(gè)8位的寄存器和一個(gè)8位的比較器組成。其中8位寄存器的初始值為0FFH,也可通過AD BUS的8位數(shù)據(jù)口和WR DOG片選口進(jìn)行置數(shù)。當(dāng)1024Hz方波進(jìn)入8位計(jì)數(shù)器進(jìn)行計(jì)數(shù)時(shí),比較器同時(shí)會(huì)將計(jì)數(shù)器的計(jì)數(shù)值與寄存器相比較,一旦兩者相等,比較器將產(chǎn)生一個(gè)REST高電平,禁止計(jì)數(shù)脈沖輸入同時(shí)打開復(fù)位電路中的計(jì)數(shù)器。仿真波形如圖3所示。

計(jì)數(shù)定時(shí)電路本文引用地址:http://www.104case.com/article/190399.htm

其中RESTCLKIN為1024Hz基準(zhǔn)時(shí)鐘輸入端。CLR為8位計(jì)數(shù)器清零端。WR為8位寄存器的片選鎖存端(上升沿鎖存)。DATA7為8位數(shù)據(jù)總線,用于預(yù)置8位寄存器。REST為復(fù)位輸出端,提供高電平以保證系統(tǒng)復(fù)位。

3.3 復(fù)位延時(shí)電路

該電路的功能由U3 DELAY12MS宏單元來完成,目的是在REST信號(hào)產(chǎn)生后,使其保持在10ms以上的穩(wěn)定高電平,以保證可以實(shí)現(xiàn)系統(tǒng)可靠地復(fù)位,并在延時(shí)結(jié)束后產(chǎn)生一個(gè)高電平將所有宏單元計(jì)數(shù)器清零。仿真波形如圖4所示。

其中,CLKIN為1024Hz基準(zhǔn)時(shí)鐘脈沖,當(dāng)U5_COMP宏單元REST輸出為高電平時(shí)被允許輸入U(xiǎn)3_DELAY12MS宏單元。當(dāng)計(jì)數(shù)器計(jì)為12時(shí),U3_DELAY12MS宏單元CLRALL端產(chǎn)生一個(gè)高電平,通過32768Hz的脈沖鎖存到D型寄存器中,D型寄存器的輸出端將會(huì)把所有計(jì)數(shù)器清零,使U5_COMP宏單元中比較器的輸出端為“0”,從而結(jié)束復(fù)位。

4 結(jié)束語

目前,本人在所設(shè)計(jì)的產(chǎn)品中都采用了這種設(shè)計(jì),實(shí)踐證明,通過CPLD器件來整合看門狗電路,將能有效地保證系統(tǒng)正常工作,同時(shí)減小單獨(dú)放置看門狗器件帶來的設(shè)計(jì)風(fēng)險(xiǎn)和額外的費(fèi)用。

評(píng)論