基于CPLD技術的看門狗電路設計

隨著現代電子技術的發展,帶有各種微處理的現代電子設備已廣泛應用于國民生產的各行各業中。但隨著設備功能越來越強大,程序結構越來越復雜,指令代碼越來越長,加之現場工作環境的干擾,設備失控,程序“走飛”,各功能模塊“死機”的概率也同樣成倍地增加。對此,常見的解決方法是在電路設計時放置一片硬件看門狗(Watchdog)電路,其目的是在系統“走死”后能強制系統復位并返回初始化程序。隨著CPLD器件被廣泛應用于各種儀器、儀表設備的設計中,而且CPLD幾乎可模擬任何一種邏輯電路,所以,現在在設計時已完全沒有必要再放置一片獨立的看門狗器件,而完全可以將硬件看門狗電路整合于CPLD器件中,從而節省成本,降低系統的設計風險。下面具體介紹這種基于CPLD技術的看門狗電路的設計。

2 工作原理

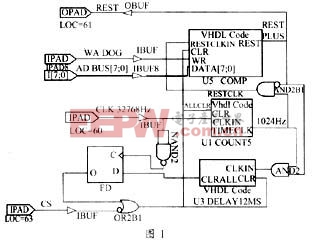

CPLD是英文Complex Programmable LogicDevice的縮寫,中文名稱為復雜可編程邏輯器件,因其具有工作效率高、內部延時小、可預測延時等特點,而被廣泛應用于計數器、邏輯電路、控制電路和復雜的狀態機等功能的實現,而看門狗電路的核心就是一個計數定時電路,所以,利用CPLD特點將能很好地實現看門狗電路的功能。看門狗電路的原理框圖如圖1所示。它在結構上可分為分頻電路、計數定時電路和復位電路三大部分,其工作方式是將一個32768Hz的方波時鐘輸入分頻電路,分頻后的方波再輸入到計數定時電路中進行計數,同時與已設置好的計數時間常數相比較,當CPU在指定的時間內沒有通過改變CS端狀態來將計數定時器清零,一旦計數值與預先設定的值相一致,計數定時電路將產生一個高電平給復位電路,復位電路將產生一個復位信號給CPU的REST端。例如,對于MCS51系列單片機來說,將產生一個大于10ms的高電平以保證CPU可靠地復位。

復雜可編程邏輯器件

3 電路設計

目前,XILINX公司的可編程器件,因其良好的設計平臺、安全的加密方法、完整的產品線,而被廣泛地應用于各種產品中。下面,以其產品線中的X95系列CPLD為例,具體介紹看門狗電路的設計。

看門狗電路的設計

3.1 分頻電路

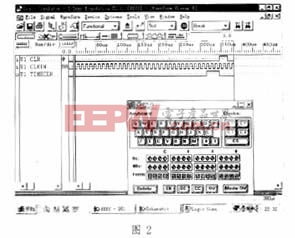

該電路是由圖1中的U1 COUNT5宏單元來完成的,該宏單元的目的是將32768kHz的矩形脈沖通過一個5位的二進制計數器,經32級分頻,得到一個1024Hz的方波,也就是周期約為1ms的方波,其仿真波形如圖2所示。

評論