基于FPGA的實時數字化光纖傳輸系統

3 軟件設計

設計采用自頂向下的模塊化設計方法,用Verilog硬件語言編程,實現FPGA對光纖接口處芯片、A/D和 D/A轉換器等外圍電路的控制。

3.1 發送端FPGA程序設計

發送端FPGA邏輯設計主要包括采樣存儲邏輯、校驗、成幀及編碼邏輯和光發送器接口邏輯。

3.1.1 采樣存儲邏輯

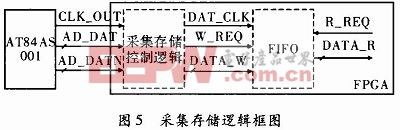

采樣存儲邏輯完成數據的采集以及實時存儲。其邏輯形式及原理框圖如圖5所示。本文引用地址:http://www.104case.com/article/190349.htm

AT84AS001是ADC芯片。輸入的差分數據直接接到FPGA的專用差分引腳。采集存儲控制邏輯包括LVDS接收以及數據重組等模塊,通過LVDS接收器將雙沿時鐘變為單沿,數據重組模塊進行數據重新排序,還原原始數據流。最后在FIFO中進行緩存。

3.1.2 校驗、成幀及編碼邏輯

校驗、成幀及編碼邏輯完成數據格式轉換,將處理后的數據進行CRC編碼、成幀、8B/10B編碼和并串轉換。算法流程如圖6所示。

3.1.3 光發送器接口邏輯

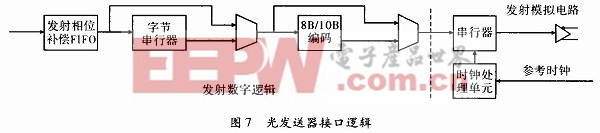

光發送器接口邏輯完成幀數據到高速串行數據流的轉換。直接利用FPGA內部的專用收發器,其結構如圖7所示。

幀數據首先南發射相位補償FIFO模塊進行相位補償,抵消時鐘相位差,然后通過字節串行器將數據轉換為8位,接著進行8B/10B編碼,并由串行器轉換為高速數據流,由專用差分輸出口輸出。

3.2 接收端FPGA程序設計

發送端FPGA邏輯設計主要包括光接收器接口邏輯和解碼、解幀及校驗邏輯。

3.2.1 光接收器接口邏輯

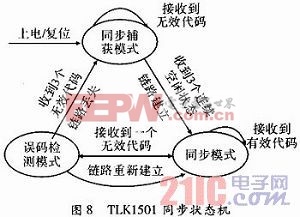

TLK1501有一個狀態機,負責監測不同的工作狀態,即同步捕獲模式、同步模式和誤碼檢測模式。上電或復位后,狀態機進入同步捕獲模式,當接收到3個連續的IDLE碼或載波擴展碼或1個有效數據或錯誤延時,即進入同步模式。在同步模式下進行數據的正常接收與發送。在這個模式下,TLK1501接收到一個無效代碼,狀態機立即進入誤碼檢測模式。檢測模式收到4個連續無效代碼時,TLK1501立即重新進入捕獲模式。TLK1501同步狀態機如圖8所示。

評論