基于FPGA和DSP的高速圖像處理系統(tǒng)

3 系統(tǒng)軟件設(shè)計

該系統(tǒng)的設(shè)計根據(jù)硬件結(jié)構(gòu)的總體劃分,也可以分為2大部分來描述。FPGA方面的軟件設(shè)計主要是各功能模塊的編寫,如攝像頭I2C配置模塊、SDRAM控制器、圖像圖像預(yù)處理器、VGA控制器、SD卡控制器、高速緩沖器等;DSP方面的設(shè)計主要包括2方面,一方面是外部存儲器驅(qū)動的編寫,如SDRAM、雙口RAM、FLASH等;另一方面為在DSP內(nèi)部實現(xiàn)高效的圖像壓縮算法,如本文采用的JPEG壓縮算法的實現(xiàn)。本文引用地址:http://www.104case.com/article/190285.htm

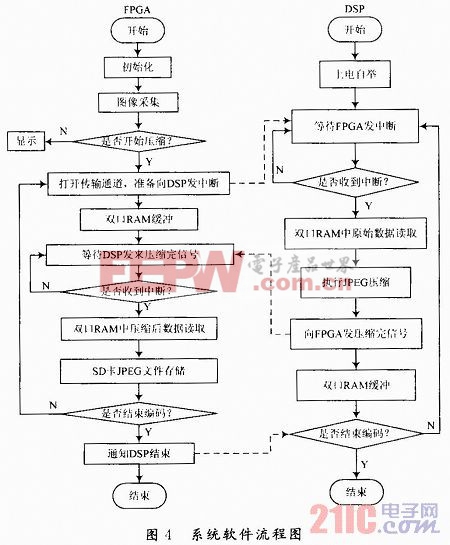

整個系統(tǒng)的程序運行如圖4所示,從高速壓縮系統(tǒng)軟件流程圖中可以清楚的看到,FPGA和DSP各自的程序運行遵循著自己的一套規(guī)則,但是它們之間的之間又實時的完成著數(shù)據(jù)的交互。FPGA向DSP方向的指令,是通過FPGA方面設(shè)置了一個中斷信號,當(dāng)DSP接受到該信號的時候,就開始從雙口RAM中按照規(guī)則進行原始數(shù)據(jù)的讀取;DSP如果要完成向FPGA方面進行數(shù)據(jù)傳輸時,遵循的一個類似的執(zhí)行規(guī)則,DSP會提供一個能夠進行辨別的信號,讓其從雙口RAM中把壓縮后的圖像數(shù)據(jù)讀進來。

4 測試結(jié)果

將FPGA上的程序下載EPCS中和將DSP開發(fā)程序燒寫進FLASH(默認(rèn)自舉方式),對實時圖像處理系統(tǒng)進行軟硬件聯(lián)合調(diào)試。設(shè)置采集和處理圖像分辨率為640×480,視頻YUV下采樣率選4:1:1,DSP中壓縮一幀圖像所用的時間在23 ms左右,壓縮比基本上在10:1~20:1的范圍內(nèi),且SNR值基本上保證在30 dB以上。23 ms的DSP壓縮時間,再加上每幀采集、傳輸和JPEG文件存儲所用的時間,大約在31 ms左右,因此系統(tǒng)整體效率上能保證對采集來的圖像做實時處理。測試結(jié)果表明系統(tǒng)的開發(fā)已經(jīng)達(dá)到預(yù)定的設(shè)計要求。

5 結(jié)論

本文基于FPGA和DSP,設(shè)計了一種結(jié)構(gòu)簡單、成本低、性能高、功耗低的高速圖像處理系統(tǒng)。在總結(jié)現(xiàn)有的FPGA與DSP高速通訊方式的基礎(chǔ)上,提出了一種利用單片雙口RAM做通信媒質(zhì)完成FPGA與DSP之間數(shù)據(jù)高速通訊的結(jié)構(gòu),為實現(xiàn)更好的嵌入式圖像處理系統(tǒng)提供了一個良好的解決方案。

fpga相關(guān)文章:fpga是什么

評論