基于FPGA的ISA總線/MMи總線數據轉換電路設計

2 硬件設計

2.1 工作原理

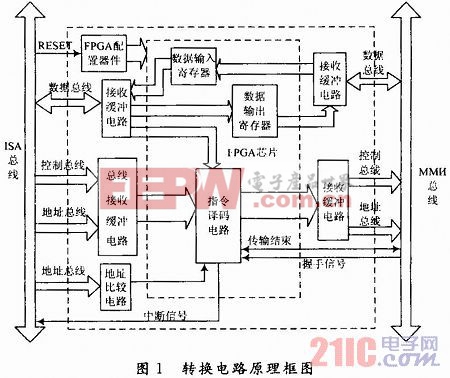

如圖1所示,轉換電路由FPGA芯片EPF10K30-RI208-4、FPGA配置器件EPC2LI20、接收緩沖電路、地址比較電路和總線接收電路組成。工作原理如下:當轉換電路工作時,首先根據FPGA配置器件內的文件對FPGA芯片進行自動配置,當ISA總線相應地址位與6位撥動開關值匹配時(撥動開關為預設待轉數據模塊地址),選中需要轉換數據的地址,然后由ISA數據總線發送數據或命令,FPGA芯片中的譯碼電路結合地址總線信號和控制總線信號將控制數據轉為MMи總線對后級程控模塊的控制指令,對后級模塊實現控制。本文引用地址:http://www.104case.com/article/190276.htm

當傳遞某MMи程控模塊的數據時,首先將MMи程控模塊初始化,然后由ISA總線發送“模塊選址”數據,寫入FPGA中地址寄存器后,經譯碼產生選址信號,并由觸發器保持。選址后,ISA總線發送“初始化”指令,寫入命令寄存器后,經譯碼產生初始化信號。當監測到“準備好”信號時,說明初始化成功,發送“清除模塊選址”信號。

MMи程控模塊接收信息時,在被尋址且發出準備好信號后,ISA總線將要寫入程控模塊的數據先寫入FPGA中的數據輸出寄存器中,然后發送到MMи數據總線上,發出“Пpиeм”接收信號,程控模塊根據此信號將數據寫入相應信息寄存器。信息接收結束后,取消“Пpиeм”接收信號,取消MMи數據總線上數據。程控模塊準備接收新的信息字節,并產生準備好的信號。

程控模塊發送信息時,在被尋址且發出準備好信號后,由ISA總線控制沿“A0~A2”線路指定接收信息寄存器地址,并發出“Bыд.”發送信號,程控模塊根據此信號從發送信息寄存器沿MMи數據總線發出信息字節,所發出的信息字節被讀取到FPGA中的數據輸入寄存器后由ISA總線控制讀出。

2.2 FPGA配置器件電路

FPGA配置器件電路如圖2所示,EPC2LI20為配置芯片,工作電壓5 V或3.3 V,支持在系統編程(ISP)和菊花鏈配置,可重復編程;EPF10K 30R1208-4為Altera公司生產FPGA芯片,工作電壓為5 V,包含邏輯單元1 728個,存儲位數12 288位;JP為通過QuartusⅡ軟件對配置芯片進行程序燒寫接口。

評論