PCB板電磁兼容設計關鍵良好的時鐘電路設計方案

在晶振和時鐘電路下面的局部地平面可以為晶振及相關電路內部產生的共模RF電流提供通路,從而使RF發射最小。為了承受流到局部地平面的共模RF電流,需要將局部地平面與系統中的其他地平面多點相連。即表層的局部地平面與系統內部地平面相連的過孔提供了到地的低阻抗。同時要注意的是要保證晶振底下地平面的完整性。使用完整地平面的信號的回流和信號本身方向相反,大小相等,能夠很好的互相抵消,可以保證其良好的信號完整性和電磁兼容特性。但是,如果地平面不完整,回流路徑中的電流與信號本身的電流不能相互抵消時(盡管這種電流不平衡有時候是不可避免的),就會產生一部分共模電流。產生的共模電壓就會激勵連接的外圍結構,造成較大的輻射。

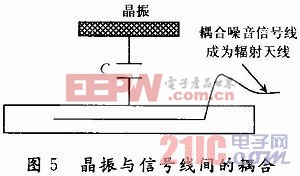

如果布線從晶振下面穿過,特別是傳輸到連接器的布線,不僅破壞局部地平面的作用,而且還會將晶振產生的噪聲通過容性耦合的方式耦合到穿過它下面的信號線,使這些信號線帶有共模電壓噪聲,如果這些信號線通過連接器又延伸出PCB,就會將噪聲帶出。這是一種典型的共模輻射問題,原理如圖5所示。

3.3 端接設計

時鐘驅動芯片不用的輸出管腳,比如:空載(開路),由于管腳開路全反射可能會引起時鐘高次諧波的電磁干擾問題。在單板上加備用端接是解決這個問題的一種方案,但是備用端接采用電阻還是電容或者其他的端接方式時主要看空載所引起的電磁干擾的頻點。如果采用電阻端接,就要考慮由此帶來的功耗和驅動器的驅動電流;如果采用電容端接,可能會增加某些其他頻點的電磁干擾,因此電容的大小時要優化電容值;如果不用管腳沒有端接,但是已經通過試驗證明了電磁干擾有足夠的裕度,就沒必要對未用管腳進行額外的備用端接處理。

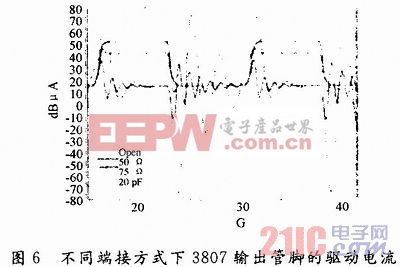

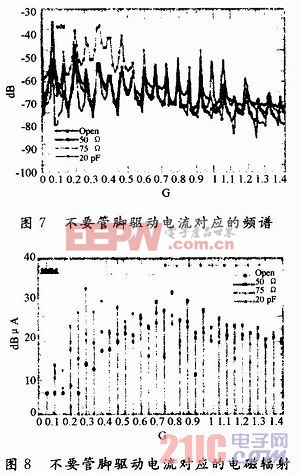

下面以3807數字時鐘芯片為例,用仿真試驗的結果來解釋備用端接的作用。圖6~圖8表示了芯片不用的輸出管腳時在開路、接50 Ω對地電阻、接75 Ω對地電阻、接20 pF對地電容等方式時,驅動腳的電流、頻譜分布及驅動電流所產生的電磁輻射。

從上面的結果可以看出:

(1)開路時的驅動電流最小,但有明顯的窄脈寬振鈴。就說明如果驅動器不用管腳空載(開路),驅動器的功耗最小。但是由此會帶來一個不利的方面,那就是驅動電流的頻譜中高頻分量會變大,有可能導致高頻的電磁干擾問題。這一點通過圖7和圖8中的開路驅動電流的頻譜和電磁干擾曲線(藍色曲線)也可以得到驗證。

評論