FPGA/CPLD中常見模塊設計精華集錦(一)

4 軟件實現

在設計的總體構思和器件選擇完成后,必須進行的工作是建立設計輸入文件,該文件主要用于描述所設計電路的邏輯功能。這里使用的是XILINX公司提供的開發工具FOUNDATION 4.1。本設計采用硬件描述語言VHDL來設計,其部分程序如下:

entity lvds is

port (

pclk: in STD LOGIC;

pclk_62: out std_logic_vector(31 downto 0);?

pclk_4: out std_logic_vector(31 downto 0));

end lvds;

architecture lvds_arch of lvds is

component clkdll

port( clkin: in std_logic;

clkfb : in std_logic;

rst: in std_logic;

clk0: out std_logic;

clk90 : out std_logic;

clk180: out std_logic;

clk270: out std_logic;

clk2x : out std_logic;

clkdv: out std_logic;

locked: out std_logic);

end component;

begin

reset n<=‘0' ;

uibuf : ibufg port map (

i => pclk,

o => clk);

udll: clkdll port map( clkin => clk,

rst => reset_n,

clkfb => clkfb,

clk0 => clk0,

clk90 => open,

clk180 => open,

clk270 => open,

clk2x => clk2x,

clkdv => clkdv,

locked => locked

);

bufg_clk0: bufg port map ( i => clk0,

o=>clk_int2;

);

clkfb<=clk_int2;

process(clk2x);

begin

if clk2x′event and clk2x=′1′ then

clk_int <=clk int2;

clk_int3<= clkdv;

pclk_62(0)<=clk_int;

pclk_62(1)<=clk_int;

…

…

pclk_62(31)<=clk_int;

pclk_4(0)<=clk_int3;

pclk_4(1)<=clk_int3;

…

…

pclk_4(31)<=clk_int3;

end if;

end process;

end lvds_arch;

四、基于FPGA的多種形式分頻的設計與實現

分頻器是數字系統設計中的基本電路,根據不同設計的需要,我們會遇到偶數分頻、奇數分頻、半整數分頻等,有時要求等占空比,有時要求非等占空比。在同一個設計中有時要求多種形式的分頻。通常由計數器或計數器的級聯構成各種形式的偶數分頻及非等占空比的奇數分頻,實現較為簡單。但對半整數分頻及等占空比的奇數分頻實現較為困難。本文利用VHDL硬件描述語言,通過QuartusⅡ3.0開發平臺,使用Altera公司的FPGA,設計了一種能夠滿足上述各種要求的較為通用的分頻器。

一、電路設計

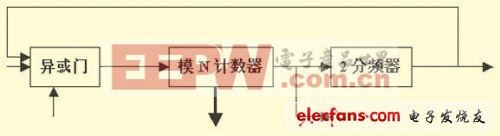

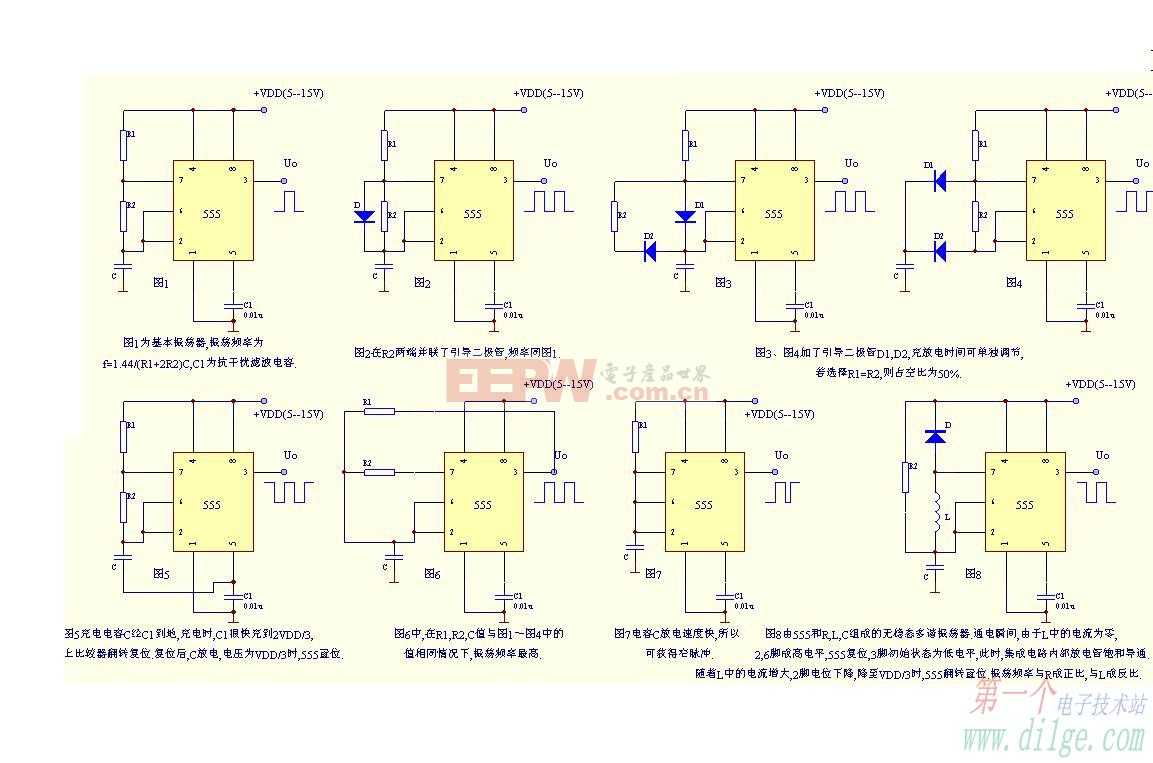

采用FPGA實現半整數分頻器,可以采用以下方法:設計一個模N的計數器,再設計一個脈沖扣除電路,每來兩個脈沖扣除一個脈沖,即可實現分頻系數為N-0.5的分頻器。脈沖扣除電路由異或門和一個2分頻器構成。本設計在半整數分頻器原理的基礎上,對異或門加一個使能控制信號,通過對異或門和計數器計數狀態值的控制,實現同一個電路完成多種形式分頻,如圖1所示。

二、VHDL語言的實現

現通過設計一個可以實現8.5分頻,等占空比的17分頻,2、4、8、16、32分頻,及占空比為1∶8和4∶5的9分頻等多種形式分頻的分頻器,介紹該通用分頻器的FPGA實現。

由圖1所示的電路原理圖可知,分頻器由帶使能端的異或門、模N計數器和一個2分頻器組成,本設計用D觸發器來完成2分頻的功能,實現方法是:將觸發器的Q反輸出端反饋回輸入端D,將計數器的一個計數輸出端作為D觸發器的時鐘輸入端。各功能模塊的VHDL語言實現如下。

1.模N計數器的實現

一般設計中用到計數器時,我們可以調用lpm庫中的計數器模塊,也可以采用VHDL語言自己設計一個模N計數器。本設計采用VHDL語言設計一個最大模值為16的計數器。輸入端口為:使能信號en,復位信號clr和時鐘信號clk;輸出端口為:qa、qb、qc、qd。其VHDL語言描述略。

2.帶使能控制的異或門的實現

輸入端為:xor_en:異或使能,a和b:異或輸入;輸出端為:c:異或輸出。當xor_en為高電平時,c輸出a和b的異或值。當xor_en為低電平時,c輸出信號b。其VHDL語言略。

3.2分頻(觸發器)的實現

輸入端為:時鐘信號clk,輸入信號d;輸出端為:q:輸出信號a,q1:輸出信號a反。其VHDL語言略。

4.分頻器的實現

本設計采用層次化的設計方法,首先設計實現分頻器電路中各組成電路元件,然后通過元件例化的方法,調用各元件,實現整個分頻器。其VHDL語言略。

三、仿真結果及硬件電路的測試

本設計的目的是通用性和簡易性,只要對上述程序稍加改動即可實現多種形式的分頻。

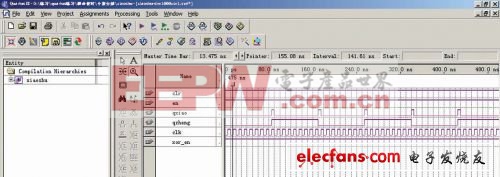

1.實現8.5分頻和等占空比的17分頻

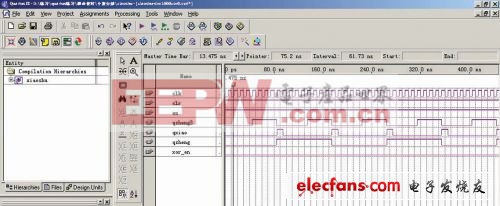

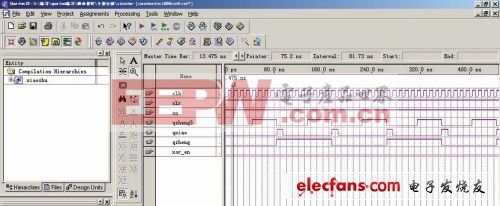

只要將上述程序中,調用計數器模塊時端口qa、qb、qc匹配為open狀態,同時置xor_en為高電平即可。從編譯報告看出總共占用8個邏輯單元(logic elements),其仿真波形如圖2~4所示。

圖二

圖三

圖四

由圖中qxiao和clk的波形可以看出,每隔8.5個時鐘周期,qxiao信號產生一個上升沿,從而實現分頻系數是8.5的分頻,同時在qzheng端得到等占空比的17分頻。設clk為170MHz,則qxiao輸出為20MHz,qzheng輸出為10MHz。

2.實現占空比為1∶8和4∶5的9分頻

只要上述程序的xor_en置低電平即可在qxiao輸出占空比為1∶8的9分頻信號;在qzheng2輸出占空比為4∶5的9分頻信號。同樣僅占8個邏輯單元(logic elements)。仿真波形如下。

3.實現等占空比的2、4、8、16和32分頻

只要將上述程序中的xor_en置為低電平,同時將計數器模塊的計數最大值設為16即可。仿真波形如下。

由此可見,只要稍微改變計數器的計數狀態值,對異或門進行選通控制,即可實現上述多種形式的分頻。本設計在Altera公司的EP1K50QC208-3構成的測試平臺上測試通過,性能良好。

結束語

我們在設計模擬雷達脈沖信號和用FPGA開發擴頻芯片時就用到了上述多種形式得分頻。本文旨在介紹一種進行FPGA開發時,所需多種分頻的實現方法,如果設計中所需分頻形式較多,可以直接利用本設計,通過對程序的稍微改動以滿足自己設計的要求。如果設計中需要分頻形式較少,可以利用本設計部分程序,以節省資源。

fpga相關文章:fpga是什么

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鑒相器相關文章:鑒相器原理 脈沖點火器相關文章:脈沖點火器原理 雙絞線傳輸器相關文章:雙絞線傳輸器原理 三相異步電動機相關文章:三相異步電動機原理 鎖相環相關文章:鎖相環原理 三維掃描儀相關文章:三維掃描儀原理

評論