基于CPLD的多DSP及FPGA遠程加載設計

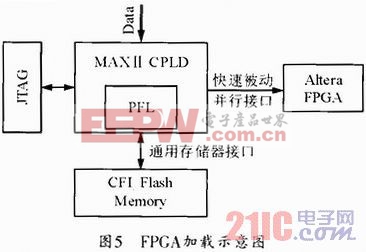

對Stratix系列的FPGA而言,加載過程相對復雜,實現起來比較困難,因為FPGA在加載過程中不僅要滿足時序控制,而且加載的數據內部還含有一定的器件信息,需要滿足消息格式和CRC校驗才能順利完成加載。而器件信息和CRC校驗方程用戶是無法得到的,因此只能采用Alte ra公司設計的MAXⅡ系列CPLD來完成加載過程。這款CPLD內部自帶一個并行加載模塊(PARALLEL FLASHLOADER),此模塊對FPCA有專用加載接口,內部嵌入了FPGA的加載控制時序及器件信息,象一道橋梁將FPCA和通用存儲器無縫連接,但硬件設計時FPGA必須設置為被動加載方式,如圖5所示。系統需要對FPGA程序重構時,只需通過邏輯啟動CPLD的PFL模塊,PFL模塊從通用存儲器中讀取配置數據,并且將配置數據進行格式轉換打包、CRC校驗后按照FPGA的加載時序寫入FPGA內部,然后上拉配置完成標志位來啟動新程序運行,實現FPGA的功能重構。本文引用地址:http://www.104case.com/article/190244.htm

利用MAXⅡ系列CPLD不僅可以實現單個FPGA程序的加載,也可以根據實際應用需求通過硬件擴展以及在CPLD中增加澤碼控制邏輯實現多個FPCA的加載。滿足系統復雜的使用要求。

3 結束語

本設計采用MAXⅡ系列CPLD作為數字處理模塊的主控芯片,來實現整個模塊工作狀態檢測、時序管理以及多個DSP芯片和FPGA芯片的程序更新升級和加載,充分利用MAXⅡ系列CLPD芯片的硬件資源、合理調用內嵌加載邏輯模塊,有效規避FPGA芯片與通用Flash芯片接口不匹配帶來的設計缺陷,簡化了FPGA芯片程序加載復雜度。不僅可以遠程控制更新重構,還可實現動態重構,這都給處理器芯片以及FPGA芯片的加載方式和應用提出了更高的要求。

本模塊已經隨某通信終端完成了試飛鑒定測試,模塊各項指標優異、遠程更新、重構功能穩定可靠,均達到了設計要求。實現了系統模塊通用化,波形功能多樣化,使用維護智能化的設計要求。

評論