基于SRAM的FPGA配置數據存儲方式解析方案

2.3.2 Slave SelectMap 模式的配置流程

Slave SelectMap 模式下提供時鐘的是外部器件,本方案中的時鐘信號是CCLK 使用 ARM 芯片的通用IO 進行模擬。同時,該模式下數據管腳有8 個,因此在每個CCLK 的上 升沿,FPGA 可以讀入1 個字節的數據。需要注意的是這1 字節的最高位是D0,而不是一 般微處理器默認的D7,在電路板布線和編寫配置程序時應給予相應改變。

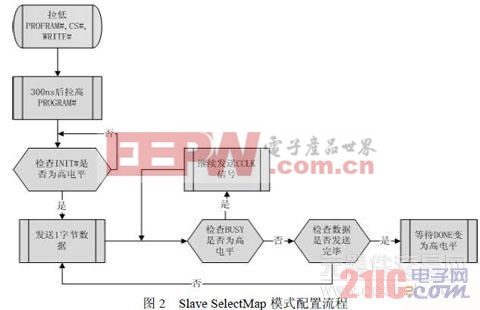

配置過程的具體流程如圖2 所示。

接收完配置數據后,DONE 管腳會被拉高。但這并不是表示配置過程已經結束,系統仍 需要時鐘來進行后續的上電啟動工作。為保證上電配置過程的正確進行,最好的辦法是將配 置文件中的所有數據寫入FPGA 中之后,然后繼續輸出CCLK 信號,直到DONE 管腳被拉 高。之后,再輸出8 個周期的CCLK,保證配置能正常完成。

根據上述流程,配置程序的主要函數的偽碼如下。

1.初始化函數SelectMAP_Init,在其它函數之前運行。

SelectMAP_Init(){

將ARM 通用IO 設置為對應的SelectMap 管腳信號;

設置 PROGRAM#,CS#和WRITE#管腳為低電平;

延時至少300ns;

設置 PROGRAM#為高電平;

循環檢查INIT#是否變為高電平;

}

評論