基于FPGA的信號頻譜分析系統

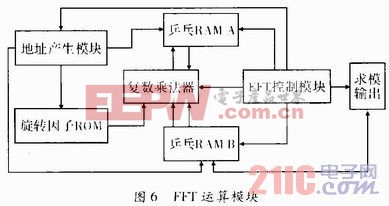

蝶形運算單元是整個FFT處理單元的重要部分,直接影響整個FFT單元性能。一個基2蝶形運算要進行1次復乘、2次復加。為提高運算速度采用并行運算,采用4個實數乘法器、3個實數加法器和3個實數減法器組成。數據格式選擇定點16位二進制補碼。設計時必須考慮乘法器速度,將會直接影響整個FFT處理單元的運算速度,乘法器的兩輸入均為16位,輸出32位。因為乘法器中帶有旋轉因子項,所以乘法運算后不應改變輸入的幅值即乘法器的輸出仍為16位,因此要對輸出數據進行截取,截取其中16位作為加法器的輸入。一個蝶形運算在一個時鐘周期內即可完成。FFT運算模塊結構如圖6所示。本文引用地址:http://www.104case.com/article/190196.htm

存儲單元包括2塊乒乓RAM、一塊RAM和一塊ROM,蝶形運算的輸入數據和輸出數據分別存儲在兩個雙口乒乓RAM中,RAM用來存儲FFT的模,旋轉因子事先計算好并存儲在ROM中。數據存入結果存儲器前,要將倒序輸出變為正序輸出。轉換方法是將地址的最高位和最低位交換,次高位與次低位交換,依次類推。

2.4 VGA顯示模塊

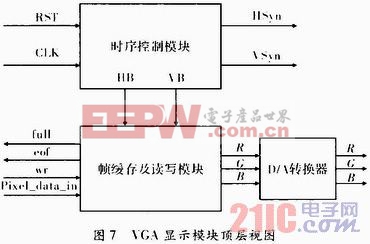

VGA顯示模塊的設計,完成的功能:(1)在一定的工作頻率下,產生正確的時序關系,即工作時鐘信號、水平同步信號(HSyn)、垂直同步信號(VSyn)、消隱信號之間的關系。(2)在正確的時序控制下讀出幀緩存中的像素數據,同時在當前幀顯示完畢時,向視頻存儲控制器發信號,使視頻存儲控制器能夠及時刷新幀緩存中的像素數據,圖7是VGA顯示模塊視圖。

其中CLK是VGA顯示模塊的時鐘信號,RST是復位信號,FULL是VGA顯示模塊中幀緩存滿標志信號,當幀緩存中數據滿時,VGA顯示模塊將此信號發送給視頻存儲控制器,WR為VGA顯示模塊中的幀緩存寫操作信號,Pixel_data_in為讀入到VGA顯示模塊的幀緩存中的像素數據,該數據來自視頻存儲器,而EOF則表明VGA顯示模塊的幀緩存已空,可以重新讀入一幀新的像素數據以供顯示。信號HSyn是由VGA顯示模塊產生的水平同步信號,發往顯示器的VGA接口,信號VSyn是由VGA顯示模塊產生的垂直同步信號,發往顯示器的VGA接口。信號尺是經D/A轉換器分離的像素數據中的紅色基色信號,發往顯示器的VGA接口,信號G是經D/A轉換器分離的像素數據中的綠色基色信號,發往顯示器的VGA接口,信號B

是經D/A轉換器分離的像素數據中的藍色基色信號,發往顯示器的VGA接口。

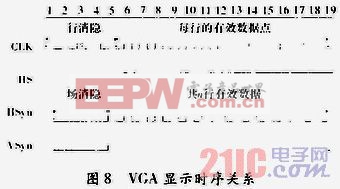

其中VGA顯示時序驅動是完成設計的關鍵。在VGA顯示控制過程中,完成一幀掃描所需要的時間成為垂直掃描時間,其倒數稱為垂直掃描頻率,又稱刷新頻率。圖8是VGA顯示的時序關系。

評論